MC9S12XDT256CAA Freescale Semiconductor, MC9S12XDT256CAA Datasheet - Page 401

MC9S12XDT256CAA

Manufacturer Part Number

MC9S12XDT256CAA

Description

IC MCU 256K FLASH 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Datasheet

1.MC9S12XD64CAA.pdf

(1348 pages)

Specifications of MC9S12XDT256CAA

Core Processor

HCS12X

Core Size

16-Bit

Speed

80MHz

Connectivity

CAN, EBI/EMI, I²C, IrDA, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

59

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Eeprom Size

4K x 8

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Processor Series

S12XD

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

16 KB

Interface Type

CAN/I2C/SCI/SPI

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

59

Number Of Timers

12

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

EVB9S12XDP512E

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12XDT256CAA

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S12XDT256CAAR

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 401 of 1348

- Download datasheet (8Mb)

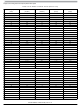

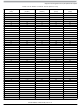

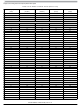

The SDA hold delay is equal to the CPU clock period multiplied by the SDA Hold value shown in

Table

The equation for SCL Hold values to generate the start and stop conditions from the IBFD bits is:

Freescale Semiconductor

MUL=1

9-5. The equation used to generate the SDA Hold value from the IBFD bits is:

SDA Hold = MUL x {scl2tap + [(SDA_Tap - 1) x tap2tap] + 3}

SCL Hold(start) = MUL x [scl2start + (SCL_Tap - 1) x tap2tap]

SCL Hold(stop) = MUL x [scl2stop + (SCL_Tap - 1) x tap2tap]

IBC[7:0]

(hex)

0A

0B

0C

0D

0E

1A

1B

1C

1D

1E

00

01

02

03

04

05

06

07

08

09

0F

10

11

12

13

14

15

16

17

18

19

1F

20

21

22

Table 9-5. IIC Divider and Hold Values (Sheet 1 of 5)

SCL Divider

(clocks)

104

128

112

128

144

160

192

240

160

192

224

20

22

24

26

28

30

34

40

28

32

36

40

44

48

56

68

48

56

64

72

80

88

80

96

MC9S12XDP512 Data Sheet, Rev. 2.21

SDA Hold

(clocks)

10

10

11

11

13

13

13

13

17

17

21

21

17

17

25

25

33

33

17

17

33

7

7

8

8

9

9

7

7

9

9

9

9

9

9

Chapter 9 Inter-Integrated Circuit (IICV2) Block Description

SCL Hold

(start)

118

110

10

11

13

16

10

12

14

16

18

20

24

30

18

22

26

30

34

38

46

58

38

46

54

62

70

78

94

78

94

6

7

8

9

SCL Hold

(stop)

121

113

11

12

13

14

15

16

18

21

15

17

19

21

23

25

29

35

25

29

33

37

41

45

53

65

41

49

57

65

73

81

97

81

97

401

Related parts for MC9S12XDT256CAA

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

16-BIT MICROPROCESSOR FAMILY

Manufacturer:

FREESCALE [Freescale Semiconductor, Inc]

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: