MPC562MZP56 Freescale Semiconductor, MPC562MZP56 Datasheet - Page 665

MPC562MZP56

Manufacturer Part Number

MPC562MZP56

Description

IC MPU 32BIT 56MHZ PPC 388-PBGA

Manufacturer

Freescale Semiconductor

Series

MPC5xxr

Datasheet

1.MPC561MZP56.pdf

(1420 pages)

Specifications of MPC562MZP56

Core Processor

PowerPC

Core Size

32-Bit

Speed

56MHz

Connectivity

CAN, EBI/EMI, SCI, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

64

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

2.5 V ~ 2.7 V

Data Converters

A/D 32x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

388-BGA

Processor Series

MPC5xx

Core

PowerPC

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

SCI, SPI, UART

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

56

Number Of Timers

22

Operating Supply Voltage

2.6 V to 5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

2 (10 bit, 32 Channel)

For Use With

MPC564EVB - KIT EVAL FOR MPC561/562/563/564

Lead Free Status / RoHS Status

Request inventory verification / Request inventory verification

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

No

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC562MZP56

Manufacturer:

FREESCAL

Quantity:

204

Company:

Part Number:

MPC562MZP56

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MPC562MZP56

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MPC562MZP56R2

Manufacturer:

RFT

Quantity:

1 441

Company:

Part Number:

MPC562MZP56R2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 665 of 1420

- Download datasheet (11Mb)

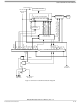

15.7.3

SCCxR1 contains SCIx configuration parameters, including transmitter and receiver enable bits, interrupt

enable bits, and operating mode enable bits. The CPU can read or write this register at any time. The SCI

can modify the RWU bit under certain circumstances.

Changing the value of SCCxR1 bits during a transfer operation can disrupt the transfer. Before changing

register values, allow the SCI to complete the current transfer, then disable the receiver and transmitter.

Freescale Semiconductor

SRESET

Bits

Field

0

1

2

3

4

5

6

7

8

9

Addr

SCI Control Register 1 (SCCxR1)

MSB

LOOPS

—

WOMS

WAKE

0

Name

TCIE

TIE

ILT

PE

PT

—

M

LOOPS WOMS ILT

1

Reserved

Loop mode

0 Normal SCI operation, no looping, feedback path disabled.

1 SCI test operation, looping, feedback path enabled.

Wired-OR mode for SCI Pins

0 If configured as an output, TXD is a normal CMOS output.

1 If configured as an output, TXD is an open drain output.

Idle-line detect type. Refer to

0 Short idle-line detect (start count on first one).

1 Long idle-line detect (start count on first one after stop bit(s)).

Parity type. Refer to

0 Even parity.

1 Odd parity.

Parity enable. Refer to

0 SCI parity disabled.

1 SCI parity enabled.

Mode select. Refer to

0 10-bit SCI frame.

1 11-bit SCI frame.

Wakeup by address mark. Refer to

0 SCI receiver awakened by idle-line detection.

1 SCI receiver awakened by address mark (last bit set).

Transmit interrupt enable

0 SCI TDRE interrupts disabled.

1 SCI TDRE interrupts enabled.

Transmit complete interrupt enable

0 SCI TC interrupts disabled.

1 SCI TC interrupts enabled.

2

Figure 15-27. SCI Control Register 1 (SCCxR1)

MPC561/MPC563 Reference Manual, Rev. 1.2

Table 15-25. SCCxR1 Bit Descriptions

3

PT

Section 15.7.7.4, “Parity

4

Section 15.7.7.2, “Serial

Section 15.7.7.4, “Parity

PE

5

0000_0000_0000_0000

Section 15.7.7.9, “Idle-Line

0x30 500A; 0x30 5022

M

6

Section 15.7.7.10, “Receiver

WAKE TIE TCIE RIE

7

Description

Checking.”

Formats.”

Checking.

8

9

Detection.”

10

Wake-Up.”

Queued Serial Multi-Channel Module

ILIE

11

TE

12

RE RWU SBK

13

14

LSB

15

15-47

Related parts for MPC562MZP56

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Mpc562 32 Bit Powerpc Microcontroller

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

MPC5 1K0 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 500R 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 5K0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 5R0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 50K 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: