AT89C51SND2C-7FTUL Atmel, AT89C51SND2C-7FTUL Datasheet - Page 135

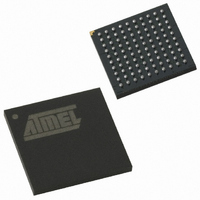

AT89C51SND2C-7FTUL

Manufacturer Part Number

AT89C51SND2C-7FTUL

Description

IC 8051 MCU FLASH 64K MP3 100BGA

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51SND2C-7FTUL.pdf

(242 pages)

Specifications of AT89C51SND2C-7FTUL

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IDE/ATAPI, MMC, SPI, UART/USART, USB

Peripherals

Audio, I²S, MP3, PCM, POR, WDT

Number Of I /o

32

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 2x10b; D/A 2x20b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

ATAPI, I2S, IDE, SPI, UART, USB

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

32

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

AT89C51SND2C7FTUL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51SND2C-7FTUL

Manufacturer:

ATMEL

Quantity:

4 371

- Current page: 135 of 242

- Download datasheet (3Mb)

18.2.1

18.2.2

4341H–MP3–10/07

Bus Lines

Bus Protocol

The bus communication uses a special protocol (MultiMedia Card bus protocol) which is applica-

ble for all devices. Therefore, the payload data transfer between the host and the cards can be

bi-directional.

The MultiMedia Card bus architecture requires all cards to be connected to the same set of

lines. No card has an individual connection to the host or other devices, which reduces the con-

nection costs of the MultiMedia Card system.

The bus lines can be divided into three groups:

•

•

•

After a power-on reset, the host must initialize the cards by a special message-based MultiMe-

dia Card bus protocol. Each message is represented by one of the following tokens:

•

•

•

Card addressing is implemented using a session address assigned during the initialization

phase, by the bus controller to all currently connected cards. Individual cards are identified by

their CID number. This method requires that every card will have an unique CID number. To

ensure uniqueness of CIDs the CID register contains 24 bits (MID and OID fields) which are

defined by the MMCA. Every card manufacturers is required to apply for an unique MID (and

optionally OID) number.

MultiMedia Card bus data transfers are composed of these tokens. One data transfer is a bus

operation. There are different types of operations. Addressed operations always contain a com-

mand and a response token. In addition, some operations have a data token, the others transfer

their information directly within the command or response structure. In this case no data token is

present in an operation. The bits on the MDAT and the MCMD lines are transferred synchronous

to the host clock.

2 types of data transfer commands are defined:

•

•

Figure 18-1 through Figure 18-5 show the different types of operations, on these figures, grayed

tokens are from host to card(s) while white tokens are from card(s) to host.

Power supply: V

Data transfer: MCMD, MDAT – used for bi-directional communication.

Clock: MCLK – used to synchronize data transfer across the bus.

Command: a command is a token which starts an operation. A command is transferred

serially from the host to the card on the MCMD line.

Response: a response is a token which is sent from an addressed card (or all connected

cards) to the host as an answer to a previously received command. It is transferred serially

on the MCMD line.

Data: data can be transferred from the card to the host or vice-versa. Data is transferred

serially on the MDAT line.

Sequential commands: These commands initiate a continuous data stream, they are

terminated only when a stop command follows on the MCMD line. This mode reduces the

command overhead to an absolute minimum.

Block-oriented commands: These commands send a data block succeeded by CRC bits.

Both read and write operations allow either single or multiple block transmission. A multiple

block transmission is terminated when a stop command follows on the MCMD line similarly

to the stream read.

SS1

and V

SS2

, V

DD

– used to supply the cards.

AT8xC51SND2C/MP3B

135

Related parts for AT89C51SND2C-7FTUL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: