MPC8309VMAHFCA Freescale Semiconductor, MPC8309VMAHFCA Datasheet - Page 6

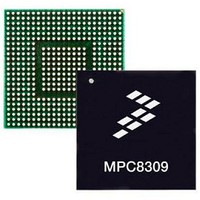

MPC8309VMAHFCA

Manufacturer Part Number

MPC8309VMAHFCA

Description

417/333/233 MP Std Tmp

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC8309VMAHFCA.pdf

(81 pages)

Specifications of MPC8309VMAHFCA

Processor Series

MPC8309

Core

e300c3

Data Bus Width

32 bit

Data Ram Size

512 MB

Interface Type

USB, CAN, UART, PCI

Maximum Clock Frequency

417 MHz

Number Of Programmable I/os

56

Operating Supply Voltage

- 0.3 V to + 1.26 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Operating Temperature Range

0 C to + 105 C

Processor To Be Evaluated

MPC8309

Supply Current (max)

5 uA

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC8309VMAHFCA

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Overview

6

•

•

•

•

MPC8309 PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

— Card bus clock frequency up to 33.33 MHz.

— Supports 1-/4-bit SD and SDIO modes, 1-/4-bit modes

— Supports block sizes of 1 ~ 4096 bytes

Universal serial bus (USB) dual-role controller

— Designed to comply with Universal Serial Bus Revision 2.0 Specification

— Supports operation as a stand-alone USB host controller

— Supports operation as a stand-alone USB device

— Supports high-speed (480-Mbps), full-speed (12-Mbps), and low-speed (1.5-Mbps) operations.

FlexCAN module

— Full implementation of the CAN protocol specification version 2.0B

— Up to 64 flexible message buffers of zero to eight bytes data length

— Powerful Rx FIFO ID filtering, capable of matching incoming IDs

— Selectable backwards compatibility with previous FlexCAN module version

— Programmable loop-back mode supporting self-test operation

— Global network time, synchronized by a specific message

— Independent of the transmission medium (an external transceiver is required)

— Short latency time due to an arbitration scheme for high-priority messages

Dual I

— Two-wire interface

— Multiple-master support

— Master or slave I

— On-chip digital filtering rejects spikes on the bus

— I

DMA Engine1

— Support for the DMA engine with the following features:

— Support for scatter/gather DMA processing

– Up to 133 Mbps data transfer for SD/SDIO/MMC cards using 4 parallel data lines

Low speed is only supported in host mode.

– Sixteen DMA channels

– All data movement via dual-address transfers: read from source, write to destination

– Transfer control descriptor (TCD) organized to support two-deep, nested transfer operations

– Channel activation via one of two methods (for both the methods, one activation per

– Support for fixed-priority and round-robin channel arbitration

– Channel completion reported via optional interrupt requests

2

C1 can be used as the boot sequencer

2

execution of the minor loop is required):

– Explicit software initiation

– Initiation via a channel-to-channel linking mechanism for continuous transfers

C interfaces

(independent channel linking at end of minor loop and/or major loop)

2

C mode support

Freescale Semiconductor