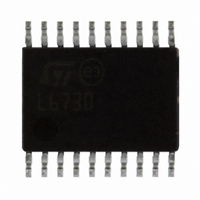

L6730C STMicroelectronics, L6730C Datasheet - Page 7

L6730C

Manufacturer Part Number

L6730C

Description

IC CTRLR ADJ STPDN SYNC 20-TSSOP

Manufacturer

STMicroelectronics

Type

Step-Down (Buck)r

Datasheet

1.L6730DTR.pdf

(50 pages)

Specifications of L6730C

Internal Switch(s)

No

Synchronous Rectifier

Yes

Number Of Outputs

1

Voltage - Output

Adj to 0.6V

Frequency - Switching

100kHz ~ 1MHz

Voltage - Input

1.8 ~ 14 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

20-TSSOP Exposed Pad, 20-eTSSOP, 20-HTSSOP

Package

HTSSOP20, QFN4x4 24L

For Use With

497-5868 - EVAL BOARD 30A 400KHZ L6730497-5501 - EVAL BOARD FOR L6730XX

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Output

-

Power - Output

-

L6730C - L6730D

3

Figure 2.

1. In the L6730D the multifunction pin is: CC/OVP/UVLO.

Table 3.

Pin n.

1

2

3

SINK/OVP/UVLO

PGOO D D ELAY

PGOO D D ELAY

Pin connections and functions

TM ASK

TM ASK

EAREF

EAREF

SINK/OVP/UVLO

Pins connection (top view)

SS/INH

SS/INH

Pins connection

SY NCH

SY NCH

PGOOD DELAY

CC/OVP/UVLO

CO MP

CO MP

GN D

GN D

OSC

OSC

FB

FB

SYNCH

L6730C

L6730D

Name

10

10

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

HTSSO P20

HTSSO P20

HTSSOP20

Connecting a capacitor between this pin and ground a delay is introduced

between the trigger of the internal PGOOD comparator and the external signal

rising edge. No delay can be introduced on the falling edge of the PGOOD

signal. The delay can be calculated with the following formula:

It is a Master-Slave pin. Two or more devices can be synchronized by simply

connecting the SYNCH pins together. The device operating with the highest

F

from the Master. The best way to synchronize devices together is to set their

F

With this pin it is possible:

– To enable-disable the sink mode current capability after SS (L6730C);

– To enable-disable the constant current OCP after SS (L6730D);

– To enable-disable the latch mode for the OVP;

– To set the UVLO threshold for the 5V BUS and 12V BUS.

The device captures the analog value present at this pin at the start-up when

V

SW

SW

CC

20

20

19

19

18

18

17

17

16

16

15

15

14

14

13

13

12

12

11

11

meets the UVLO threshold.

will be the Master. The Slave devices will operate with 180° phase shift

at the same value. If it is not used the SYNCH pin can be left floating.

V CC

V CC

PGOO D

PGOO D

V CCD R

V CCD R

PGN D

PGN D

HG ATE

HG ATE

PH ASE

PH ASE

LGA TE

LGA TE

BOO T

BOO T

O CL

O CL

OCH

OCH

PGDelay

Description

0

5 .

C

pF

QFN 4x4 24L

Pin connections and functions

s]

7/50