STEVAL-IFS001V1 STMicroelectronics, STEVAL-IFS001V1 Datasheet - Page 18

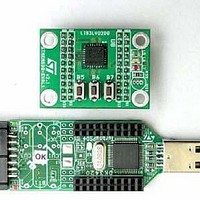

STEVAL-IFS001V1

Manufacturer Part Number

STEVAL-IFS001V1

Description

EVAL BOARD 3AXIS MEMS ACCELLRMTR

Manufacturer

STMicroelectronics

Series

MEMSr

Datasheets

1.STEVAL-IFS001V1.pdf

(42 pages)

2.STEVAL-IFS001V1.pdf

(14 pages)

3.STEVAL-IFS001V1.pdf

(4 pages)

4.STEVAL-IFS001V1.pdf

(14 pages)

Specifications of STEVAL-IFS001V1

Design Resources

STEVAL-IFS001V1 Gerber Files STEVAL-IFS001V1 Schematic STEVAL-IFS001V1 Bill of Material

Sensor Type

Accelerometer, 3 Axis

Sensing Range

±2g, 6g

Interface

I²C, SPI

Sensitivity

1024 LSb/g

Voltage - Supply

2.16 V ~ 3.6 V

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

LIS3LV02DQ

Processor To Be Evaluated

LIS3LV02DQ

Interface Type

USB

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

497-5069

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

5 Digital Interfaces

5.1.1

18/42

I

The transaction on the bus is started through a START (ST) signal. A START condition is

defined as a HIGH to LOW transition on the data line while the SCL line is held HIGH. After this

has been transmitted by the Master, the bus is considered busy. The next byte of data

transmitted after the start condition contains the address of the slave in the first 7 bits and the

eighth bit tells whether the Master is receiving data from the slave or transmitting data to the

slave. When an address is sent, each device in the system compares the first seven bits after a

start condition with its address. If they match, the device considers itself addressed by the

Master. The Slave ADdress (SAD) associated to the LIS3LV02DQ is 0011101b.

Data transfer with acknowledge is mandatory. The transmitter must release the SDA line during

the acknowledge pulse. The receiver must then pull the data line LOW so that it remains stable

low during the HIGH period of the acknowledge clock pulse. A receiver which has been

addressed is obliged to generate an acknowledge after each byte of data has been received.

The I

protocol must be adhered to. After the start condition (ST) a salve address is sent, once a slave

acknowledge (SAK) has been returned, a 8-bit sub-address will be transmitted: the 7 LSb

represent the actual register address while the MSB enables address auto increment. If the

MSb of the SUB field is 1, the SUB (register address) will be automatically incremented to allow

multiple data read/write.

The slave address is completed with a Read/Write bit. If the bit was ‘1’ (Read), a repeated

START (SR) condition will have to be issued after the two sub-address bytes; if the bit is ‘0’

(Write) the Master will transmit to the slave with direction unchanged.

Transfer when Master is writing one byte to slave

Transfer when Master is writing multiple bytes to slave:

Transfer when Master is receiving (reading) one byte of data from slave:

Transfer when Master is receiving (reading) multiple bytes of data from slave

Data are transmitted in byte format (DATA). Each data transfer contains 8 bits. The number of

bytes transferred per transfer is unlimited. Data is transferred with the Most Significant bit (MSb)

first. If a receiver can’t receive another complete byte of data until it has performed some other

2

Master

Master

Master

Slave

C Operation

Slave

Slave

Master

Slave

2

Master

Slave

C embedded inside the LIS3LV02DQ behaves like a slave device and the following

ST

ST

ST

ST

SAD + W

SAD + W

SAD + W

DATA

SAD + W

SAK

SAK

SAK

SUB

SUB

CD00047926

SAK

SUB

MAK

SAK

SAK

SAK

SUB

SR

SR

SAD + R

DATA

DATA

SAK

SAD + R

SAK

SAK

DATA

SAK

NMAK

DATA

DATA

DATA

SAK

LIS3LV02DQ

NMAK

SAK

SP

MAK

SP

SP

SP