C8051F562-IQ Silicon Laboratories Inc, C8051F562-IQ Datasheet - Page 160

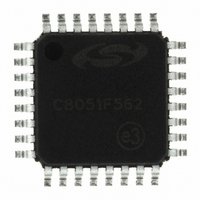

C8051F562-IQ

Manufacturer Part Number

C8051F562-IQ

Description

IC 8051 MCU 32K FLASH 32-QFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F56xr

Specifications of C8051F562-IQ

Program Memory Type

FLASH

Program Memory Size

32KB (32K x 8)

Package / Case

32-QFP

Core Processor

8051

Core Size

8-Bit

Speed

50MHz

Connectivity

SMBus (2-Wire/I²C), LIN, SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.25 V

Data Converters

A/D 25x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 125°C

Processor Series

C8051F5x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2304 B

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

25

Operating Supply Voltage

1.8 V to 5.25 V

Maximum Operating Temperature

+ 125 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F560DK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1691 - KIT DEVELOPMENT FOR C8051F560

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1698

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F562-IQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Company:

Part Number:

C8051F562-IQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

- Current page: 160 of 302

- Download datasheet (3Mb)

C8051F55x/56x/57x

18.3. Clock Multiplier

The Clock Multiplier generates an output clock which is 4 times the input clock frequency scaled by a pro-

grammable factor of 1, 2/3, 2/4 (or 1/2), 2/5, 2/6 (or 1/3), or 2/7. The Clock Multiplier’s input can be

selected from the external oscillator, or the internal or external oscillators divided by 2. This produces three

possible base outputs which can be scaled by a programmable factor: Internal Oscillator x 2, External

Oscillator x 2, or External Oscillator x 4. See Section 18.1 on page 155 for details on system clock selec-

tion.

The Clock Multiplier is configured via the CLKMUL register (SFR Definition 18.5). The procedure for con-

figuring and enabling the Clock Multiplier is as follows:

1. Reset the Multiplier by writing 0x00 to register CLKMUL.

2. Select the Multiplier input source via the MULSEL bits.

3. Select the Multiplier output scaling factor via the MULDIV bits

4. Enable the Multiplier with the MULEN bit (CLKMUL | = 0x80).

5. Delay for >5 µs.

6. Initialize the Multiplier with the MULINIT bit (CLKMUL | = 0xC0).

7. Poll for MULRDY > 1.

Important Note : When using an external oscillator as the input to the Clock Multiplier, the external source

must be enabled and stable before the Multiplier is initialized. See “18.4. External Oscillator Drive Circuit”

on page 162 for details on selecting an external oscillator source.

The Clock Multiplier allows faster operation of the CIP-51 core and is intended to generate an output fre-

quency between 25 and 50 MHz. The clock multiplier can also be used with slow input clocks. However, if

the clock is below the minimum Clock Multiplier input frequency (FCM

of four fast pulses followed by a long delay until the next input clock rising edge. The average frequency of

the output is equal to 4x the input, but the instantaneous frequency may be faster. See Figure 18.2 below

for more information.

160

if F

if F

CM

CM

in

in

< F

>= F

F

F

F

F

CM in

CM out

CM in

CM out

CM min

CM min

Figure 18.2. Example Clock Multiplier Output

Rev. 1.1

min

), the generated clock will consist

Related parts for C8051F562-IQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc