ST72F264G2B6 STMicroelectronics, ST72F264G2B6 Datasheet - Page 2

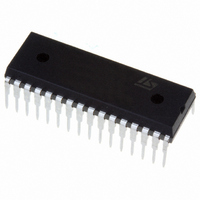

ST72F264G2B6

Manufacturer Part Number

ST72F264G2B6

Description

MCU 8-BIT 8K FLASH 32-SDIP

Manufacturer

STMicroelectronics

Series

ST7r

Specifications of ST72F264G2B6

Mfg Application Notes

ST7 Checksum Capability, AN1070 App Note

Core Processor

ST7

Core Size

8-Bit

Speed

16MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-SDIP (0.400", 10.16mm)

Processor Series

ST72F2x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

22

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7F264-IND/USB, ST72F34X-SK/RAIS, ST7MDT10-DVP3, ST7MDT10-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 6 Channel

For Use With

497-6423 - BOARD EVAL BASED ON ST72264G1497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

497-5570

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F264G2B6

Manufacturer:

ST

Quantity:

10

Company:

Part Number:

ST72F264G2B6

Manufacturer:

NEC

Quantity:

6 097

Part Number:

ST72F264G2B6

Manufacturer:

ST

Quantity:

20 000

1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 REGISTER & MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4 FLASH PROGRAM MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

6 SUPPLY, RESET AND CLOCK MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

8 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

9 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

10 MISCELLANEOUS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

2/172

4.1

4.2

4.3

4.4

4.5

4.6

4.7

5.1

5.2

5.3

6.1

6.2

6.3

6.4

7.1

7.2

7.3

7.4

7.5

8.1

8.2

8.3

8.4

8.5

9.1

9.2

9.3

9.4

9.5

9.6

9.7

9.8

2

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

PROGRAMMING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

ICC INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

MEMORY PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

RELATED DOCUMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

PHASE LOCKED LOOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

MULTI-OSCILLATOR (MO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

RESET SEQUENCE MANAGER (RSM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

SYSTEM INTEGRITY MANAGEMENT (SI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

MASKING AND PROCESSING FLOW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

INTERRUPTS AND LOW POWER MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

CONCURRENT & NESTED MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

INTERRUPT REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

SLOW MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

WAIT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

ACTIVE-HALT AND HALT MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

I/O PORT IMPLEMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

UNUSED I/O PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

LOW POWER MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

DEVICE-SPECIFIC I/O PORT CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

I/O PORT REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table of Contents

172