MCP604-I/P Microchip Technology, MCP604-I/P Datasheet - Page 12

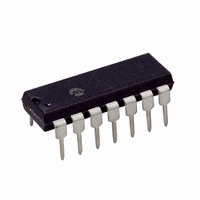

MCP604-I/P

Manufacturer Part Number

MCP604-I/P

Description

IC OPAMP QUAD SNGL SUPPLY 14DIP

Manufacturer

Microchip Technology

Specifications of MCP604-I/P

Slew Rate

2.3 V/µs

Package / Case

14-DIP (0.300", 7.62mm)

Amplifier Type

General Purpose

Number Of Circuits

4

Output Type

Rail-to-Rail

Gain Bandwidth Product

2.8MHz

Current - Input Bias

1pA

Voltage - Input Offset

700µV

Current - Supply

230µA

Current - Output / Channel

22mA

Voltage - Supply, Single/dual (±)

2.7 V ~ 6 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Number Of Channels

4

Common Mode Rejection Ratio (min)

75 dB

Input Offset Voltage

2 mV

Input Bias Current (max)

60 pA

Operating Supply Voltage

3 V, 5 V

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

Through Hole

Shutdown

No

Supply Voltage (max)

6 V

Supply Voltage (min)

2.7 V

Technology

CMOS

Voltage Gain Db

115 dB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

-3db Bandwidth

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCP604-I/P

Manufacturer:

MICROCHIP

Quantity:

12 000

Part Number:

MCP604-I/P

Manufacturer:

MICROCHIP/微芯

Quantity:

20 000

MCP601/1R/2/3/4

4.0

The MCP601/1R/2/3/4 family of op amps are fabricated

on Microchip’s state-of-the-art CMOS process. They

are unity-gain stable and suitable for a wide range of

general purpose applications.

4.1

4.1.1

The MCP601/1R/2/3/4 op amp is designed to prevent

phase reversal when the input pins exceed the supply

voltages.

exceeding the supply voltage without any phase

reversal.

4.1.2

The ESD protection on the inputs can be depicted as

shown in

protect the input transistors, and to minimize input bias

current (I

when they try to go more than one diode drop below

V

above V

allow normal operation, and low enough to bypass

quick ESD events within the specified limits.

FIGURE 4-1:

Structures.

In order to prevent damage and/or improper operation

of these op amps, the circuit they are in must limit the

currents and voltages at the V

Absolute Maximum Ratings † at the beginning of

Section 1.0 “Electrical Characteristics”).

shows the recommended approach to protecting these

inputs. The internal ESD diodes prevent the input pins

(V

the resistors R

out of the input pins. Diodes D

input pins (V

V

implemented as shown, resistors R

the current through D

DS21314G-page 12

SS

DD

IN

. They also clamp any voltages that go too far

+ and V

, and dump any currents onto V

V

V

V

IN

DD

SS

+

DD

APPLICATIONS INFORMATION

Inputs

B

). The input ESD diodes clamp the inputs

Figure

; their breakdown voltage is high enough to

Figure 2-34

Bond

Bond

Bond

PHASE REVERSAL

INPUT VOLTAGE AND CURRENT

LIMITS

Pad

Pad

Pad

IN

IN

–) from going too far below ground, and

1

+ and V

and R

4-1. This structure was chosen to

1

2

Simplified Analog Input ESD

and D

limit the possible current drawn

IN

Stage

Input

shows

–) from going too far above

2

.

IN

1

+ and V

the

and D

1

and R

Bond

Pad

input

2

IN

prevent the

– pins (see

DD

2

Figure 4-2

V

also limit

. When

IN

voltage

–

FIGURE 4-2:

Inputs.

It is also possible to connect the diodes to the left of

resistors R

diodes D

mechanism. The resistors then serve as in-rush current

limiters; the DC current into the input pins (V

V

A significant amount of current can flow out of the

inputs when the common mode voltage (V

ground (V

high impedance may need to limit the useable voltage

range.

4.1.3

The Common Mode Input Voltage Range (V

includes ground in single-supply systems (V

does not include V

input behaves linearly as long as the Common Mode

Input Voltage (V

limits (V

Figure 4-3

same voltage as the inverting input, V

below V

FIGURE 4-3:

Limited V

IN

–) should be very small.

V

V

1

2

SS

DD

1

V

SS

–0.3V to V

OUT

–1.2V for correct operation.

shows a unity gain buffer. Since V

1

and D

IN

NORMAL OPERATION

); see

R

R

and R

R

R

1

2

Range.

D

1

2

>

>

CM

2

1

V

V

2

needs to be limited by some other

) is kept within the specified V

SS

SS

DD

+

–

Figure

. In this case, current through the

MCP60X

DD

D

. This means that the amplifier

Protecting the Analog

Unity Gain Buffer has a

– (minimum expected V

– (minimum expected V

2

–1.2V at +25°C).

© 2007 Microchip Technology Inc.

2-34. Applications that are

MCP60X

2 mA

2 mA

V

R

DD

3

OUT

V

OUT

must be kept

CM

OUT

) is below

SS

1

2

IN

)

)

+ and

), but

is the

CMR

CMR

)