EVAL-ADF7020-1DB5 Analog Devices Inc, EVAL-ADF7020-1DB5 Datasheet - Page 12

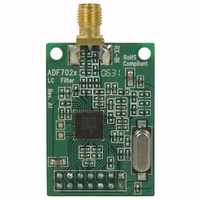

EVAL-ADF7020-1DB5

Manufacturer Part Number

EVAL-ADF7020-1DB5

Description

BOARD EVAL ADF7020-2 ADJ FREQ

Manufacturer

Analog Devices Inc

Datasheet

1.EVAL-ADF7020-1DB5.pdf

(19 pages)

Specifications of EVAL-ADF7020-1DB5

Module/board Type

Evaluation Board

For Use With/related Products

ADF7020 650MHz

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

EVAL-ADF7020-XDBX

SETTING PLL LOOP BANDWIDTHS

The Eval Boards have been built using a 50kHz PLL LBW. From

measurements made on SNR and modulation quality of the FSK

signal, it is recommended to use a LBW > 1.5 x Datarate.

So for the defulat filter on the Eval Board, this gives a max.

datarate close to 38.4kbps. If you want to operate the board at

higher data-rates you need to modify the loop filter according

Note: Need to set VCO_Adjust=0 to give correct Kvco

Table 3:ADF7020DB2/3 Filter (433M/868MHz)

11.0592M

11.0592M

11.0592M

11.0592M

Notes:

1. Deviation typ. +/- (Baud-rate/2)

2. Xtal frequency needs to be chosen so that CDR_CLK is within 3% of (32 x Data-rate). For example if you have 12MHz xtal and want

180kbps, allowable range is 181.87kbps to 193.125kbps, need to adjust data-rate or xtal accordingly

3. For filter designed with 12MHz xtal (11.0592MHz should have minimal effect on phase margin)

4. Nmin=31, so for 433MHz => PFDmax=13.96MHz

11.0592M

11.0592M

11.0592M

11.0592M

14.7456M

14.7456M

14.7456M

14.7456M

14.7456M

14.7456M

14.7456M

14.7456M

Xtal

Xtal

76.8 - 153.6kbps

153.6 - 200 kbps

76.8 - 153.6kbps

153.6 - 200 kbps

76.8 - 153.6kbps

153.6 - 200 kbps

76.8 - 153.6kbps

153.6 - 200 kbps

38.4 - 76.8 kbps

38.4 - 76.8 kbps

38.4 - 76.8 kbps

38.4 - 76.8 kbps

0.3 – 38.4kbps

0.3 – 38.4kbps

0.3 - 38.4kbps

0.3 - 38.4kbps

Data Rate

Data Rate

PLL LBW

PLL LBW

115k

215k

250k

115k

215k

250k

115k

215k

250k

115k

215k

250k

50k

50k

50k

50k

Table 2: ADF7020DB1 FILTER (902-928MHZ

Channel

Spacing

Channel

Spacing

150kHz

200kHz

500kHz

500kHz

150kHz

200kHz

500kHz

500kHz

150kHz

200kHz

500kHz

500kHz

150kHz

200kHz

500kHz

500kHz

Min

Min

2 (See Note4)

Rev. Pr C | Page 12 of 19

R Divider

Divider

R

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

1.44mA

to the values in Tables 2 & 3 for the ADF7020. For the

ADF7020-1 it is recommended to use ADIismPLL to design the

loop filter.

ADISimPLL V3.0 allows you to simulate these effects and

design loop filters for various data-rates and different RF

Output frequencies.. For output frequency/xtal/data-rate

combinations not covered below you should use ADISimPLL

V3.0 (or later).

Icp

Icp

560pF

150pF

100pF

560pF

150pF

120pF

470pF

270pF

270pF

150pF

1.5nF

2.7nF

3.3nF

1.8nF

1.8nF

1.2nF

C18

C18

)

Preliminary Technical Data

180r

680r

220r

510r

180r

220r

430r

620r

270r

360r

750r

1.3k

1.5k

1.1k

R5

R5

1k

1k

5.6nF

1.5nF

1.2nF

8.2nF

2.2nF

1.8nF

6.8nF

3.3nF

3.3nF

2.2nF

33nF

39nF

56nF

22nF

22nF

15nF

C17

C17

910r

470r

470r

470r

910r

560r

750r

1.2k

2.5k

1.2k

2.2k

2.5k

1.2k

1.5k

R4

R4

3k

2k

270pF

180pF

220pF

680pF

220pF

120pF

820pF

470pF

120pF

1.2nF

1.2nF

30pF

27pF

56pF

39pF

68pF

C16

C16