MAX98088EWY+T Maxim Integrated Products, MAX98088EWY+T Datasheet - Page 55

MAX98088EWY+T

Manufacturer Part Number

MAX98088EWY+T

Description

Audio CODECs DUAL I2S CODEC AUDIO STEREO

Manufacturer

Maxim Integrated Products

Datasheet

1.MAX98088EWYT.pdf

(123 pages)

Specifications of MAX98088EWY+T

Number Of Adc Inputs

2

Number Of Dac Outputs

2

Resolution

24 bit

Operating Supply Voltage

1.8 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Package / Case

WLP-63

Number Of Channels

2

Supply Current

4.5 mA

Thd Plus Noise

- 77 dB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

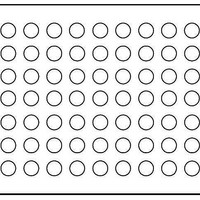

PIN

G1

G2

G3

G4

G5

G6

G7

G8

G9

E5

E6

E7

E8

E9

F1

F2

F3

F4

F5

F6

F7

F8

F9

DIGMICDATA

DIGMICCLK

JACKSNS

SDOUTS2

EXTMICN

LRCLKS2

EXTMICP

MICBIAS

DVDDS2

BCLKS2

MIC1N/

SDINS2

MIC1P/

MIC2N

MIC2P

NAME

DGND

AGND

DVDD

AVDD

INA2/

INA1/

INB1

SDA

REG

SCL

IRQ

REF

Hardware Interrupt Output. IRQ can be programmed to pull low when bits in status register

0x00 change state. Read status register 0x00 to clear IRQ once set. Repeat faults have

no effect on IRQ until it is cleared by reading the I

pullup resistor to DVDD for full output swing.

Jack Sense. Detects the insertion of a jack. See the Jack Detection section.

Single-Ended Line Input B1. Also negative differential line input B.

Positive Differential Microphone 1 Input. AC-couple a microphone with a series 1FF

capacitor. Can be retasked as a digital microphone data input.

Single-Ended Line Input A2. Also positive differential line input A or negative differential

external microphone input.

Digital Ground

S2 Digital Audio Bit Clock Input/Output. BCLKS2 is an input when the IC is in slave mode

and an output when in master mode. The input/output voltage is referenced to DVDDS2.

S2 Digital Audio Left-Right Clock Input/Output. LRCLKS2 is the audio sample rate clock

and determines whether audio data on S2 is routed to the left or right channel. In TDM

mode, LRCLKS2 is a frame sync pulse. LRCLKS2 is an input when the IC is in slave mode

and an output when in master mode. The input/output voltage is referenced to DVDDS2.

I

I

Common-Mode Voltage Reference. Bypass to AGND with a 1FF capacitor.

Low-Noise Bias Voltage. Outputs a 2.2V microphone bias. An external resistor in the 2.2kI

to 1kI range should be used to set the microphone current.

Negative Differential Microphone 1 Input. AC-couple a microphone with a series 1FF

capacitor. Can be retasked as a digital microphone clock output.

Single-Ended Line Input A1. Also negative differential line input A or positive differential

external microphone input.

S2 Digital Audio Serial-Data ADC Output. The output voltage is referenced to DVDDS2.

S2 Digital Audio Interface Power-Supply Input. Bypass to DGND with a 1FF capacitor.

S2 Digital Audio Serial-Data DAC Input. The input voltage is referenced to DVDDS2.

Digital Power Supply. Supply for the digital core and I

1FF capacitor.

Analog Power Supply. Bypass to AGND with a 1FF capacitor.

Converter Reference. Bypass to AGND with a 2.2FF capacitor.

Analog Ground

Negative Differential Microphone 2 Input. AC-couple a microphone with a series 1FF

capacitor.

Positive Differential Microphone 2 Input. AC-couple a microphone with a series 1FF

capacitor.

2

2

C Serial-Data Input/Output. Connect a pullup resistor to DVDD for full output swing.

C Serial-Clock Input. Connect a pullup resistor to DVDD for full output swing.

with FlexSound Technology

Stereo Audio Codec

FUNCTION

Pin Description (continued)

2

C status register 0x00. Connect a 10kI

2

C interface. Bypass to DGND with a

55