DAC0854BIN National Semiconductor, DAC0854BIN Datasheet - Page 4

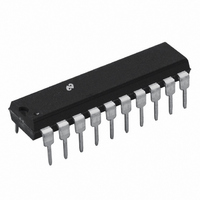

DAC0854BIN

Manufacturer Part Number

DAC0854BIN

Description

IC DAC QUAD 8BIT SERIAL 20-DIP

Manufacturer

National Semiconductor

Datasheet

1.DAC0854BIN.pdf

(14 pages)

Specifications of DAC0854BIN

Settling Time

1.5µs

Number Of Bits

8

Data Interface

MICROWIRE™, Serial

Number Of Converters

4

Voltage Supply Source

Analog and Digital

Power Dissipation (max)

95mW

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Package / Case

*

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

*DAC0854BIN

AC ELECTRICAL CHARACTERISTICS (Continued)

Converter Electrical Characteristics

The following specifications apply for AV

the analog outputs – pins 1 11 14 and 19) and f

Note 1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is

functional These ratings do not guarantee specific performance limits however For guaranteed specifications and test conditions see the Converter Electrical

Characteristics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not

operated under the listed test conditions

Note 2 All voltages are measured with respect to ground unless otherwise specified

Note 3 When the input voltage (V

to 5 mA or less

Note 4 The sum of the currents at all pins that are driven beyond the power supply voltages should not exceed 20 mA

Note 5 The maximum power dissipation must be derated at elevated temperatures and is dictated by T

(package junction to ambient thermal resistance) and T

P

packages and versions of the DAC0854

Note 6 Human body model 100 pF discharged through a 1 5 k

Note 7 See AN450 ‘‘Surface Mounting Methods and Their Effect on Production Reliability’’ of the section titled ‘‘Surface Mount’’ found in any current Linear

Databook for other methods of soldering surface mount devices

Note 8 Typicals are at T

Note 9 Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level)

Note 10 A monotonicity of 8 bits for the DAC0854 means that the output voltage changes in the same direction (or remains constant) for each increase in the input

code

Note 11 Integral linearity error is the maximum deviation of the output from the line drawn between zero and full-scale (excluding the effects of zero error and full-

scale error)

Note 12 Full-scale error is measured as the deviation from the ideal 2 800V full-scale output when V

Note 13 Full-scale error tempco and zero error tempco are defined by the following equation

where Error (T

voltage span of the DAC0854 which depends on V

Note 14 Zero error is measured as the deviation from the ideal 0 310V output when V

Note 15 Power Supply Sensitivity is the maximum change in the offset error or the full-scale error when the power supply differs from its optimum 5V by up to

0 25V (5%) The load resistor R

Note 16 Positive or negative settling time is defined as the time taken for the output of the DAC to settle to its final full-scale or zero output to within

This time shall be referenced to the 50% point of the positive edge of CS which initiates the update of the analog outputs

Note 17 Digital crosstalk is the glitch measured on the output of one DAC while applying an all 0s to all 1s transition at the input of the other DACs

Note 18 All DACs have full-scale outputs latched and DI is clocked with no update of the DAC outputs The glitch is then measured on the DAC outputs

Note 19 Clock feedthrough is measured for each DAC with its output at full-scale The serial clock is then applied to the DAC at a frequency of 10 MHz and the

glitch on each DAC full-scale output is measured

Note 20 Channel-to-channel isolation is a measure of the effect of a change in one DAC’s output on the output of another DAC The V

between 1 4V and 2 65V at a frequency of 15 kHz while the change in full-scale output of the second DAC is measured The first DAC is loaded with all 0s

Note 21 Glitch energy is the difference between the positive and negative glitch areas at the output of the DAC when a 1 LSB digital input code change is applied

to the input The glitch energy will have its largest value at one of the three major transitions The peak value of the maximum glitch is separately specified

Note 22 Power Supply Rejection Ratio is measured by varying AV

of this signal imposed on a full-scale output of the DAC under consideration

Note 23 The bandgap reference tempco is defined by the following equation

where T

Note 24 A Military RETS specification is available upon request

e

Dmax

Symbol

t

t

t

t

CZ1

CZ0

1H

0H

T

J

e

ROOM

from T

(T

Jmax

MAX

e

b

25 C V

MIN

) is the zero error or full-scale error at T

T

A

)

to T

J

REF

Output Hi-Z to Valid 1

Output Hi-Z to Valid 0

CS to Output Hi-Z

CS to Output Hi-Z

JA

e

or the number given in the Absolute Maximum Ratings whichever is lower The table below details T

25 C and represent most likely parametric norm

(T

MAX

Parameter

L

MAX

IN

e

) at any pin exceeds the power supply rails (V

) is the reference output at T

5 k

All other limits apply for T

DAC0854BIN DAC0854CIN

DAC0854BIJ DAC0854CIJ

DAC0854BIWM DAC0854CIWM

DAC0854CMJ 883

Error tempco

Tempco

CC

BIAS

e

Part Number

and V

MAX

e

DV

e

A

CC

(in volts) and Error (T

REF

V

CLK

REF

(ambient temperature) The maximum allowable power dissipation at any temperature is

Error (T

MAX

10 k

10 k

CC

e

resistor

(T

e

Conditions

e

V

5V V

MAX

and similarly for V

REF

A

DV

MAX

10 MHz unless otherwise specified Boldface limits apply for T

e

with 60 pF

with 60 pF

)

CC

(T

V

b

)

SPAN

(Continued)

REF

ROOM

25 C

b

between 4 75V and 5 25V with a frequency of 10 kHz and measuring the proportion

V

4

REF

IN k

Error (T

e

)

MIN

(T

GND or V

T

2 65V V

MIN

Jmax

REF

) is the zero error or full-scale error at T

MIN

REF

125

125

125

150

)

)

e

( C)

(T

2 650V V

IN l

MIN

T

BIAS

MAX

T

) and V

MAX

(Note 3)

V

Typical

10

a

REF

b

10

e

) the absolute value of current at that pin should be limited

6

b

BIAS

JA

T

6

REF

MIN

e

T

1 4V R

( C W)

46

53

64

53

MIN

2 650V and V

e

(T

1 400V and the digital input word is all zeros

ROOM

Jmax

L

e

)

(maximum junction temperature)

2 k

BIAS

(Note 4)

Limit

130

117

37

42

MIN

e

(R

1 400V

(in volts) V

L

Jmax

REF

is the load resistor on

of the first DAC is varied

and

SPAN

JA

for the various

ns (max)

ns (max)

ns (max)

ns (max)

(Limits)

is the output

Units

g

0 5 LSB

JA

A