SDA9290-5 Siemens Semiconductor Group, SDA9290-5 Datasheet

SDA9290-5

Available stocks

Related parts for SDA9290-5

SDA9290-5 Summary of contents

Page 1

Picture Processor Preliminary Data Features Noise and cross color reduction by field - or frame recursive filtering 3 adjustments: 4-dB-, 7-dB- or 12-dB reduction Automatic adaption to signal quality during vertical blanking Pixel adaptive movement detection Split screen modes for ...

Page 2

The necessary decimation and interpolation operations are activated automatically when the format is set. Together with a corresponding Memory Sync Controller (SDA 9220) it enables functions like multi-picture, tuner scanning, picture-in-still and still-in-picture. The different modes can be activated by ...

Page 3

Multi-Picture Processor Signals are processed in the 4:1:1 format. The vertical-decimation line memory now operates with 208 (formerly 216) pixels per line to adapt the 1/9th picture format to the new picture memory with TV-SAMs. Gray frame generation is similarly ...

Page 4

I C Bus Interface Bus interface configured as a “slave receiver” is used for programming the different functions and modes of the picture processor. Via this interface up to four registers can be written according ...

Page 5

Register R0: This control register sets the operating mode of the picture processor. Bits D7, D6: Mode Normal Multi-picture (MP) Still-in-picture (SIP) Picture-in still (PIS) Bit D5: MPP: Narrow Frame Without narrow frame With narrow frame Bit D4: No function; ...

Page 6

Register R1: This control register sets the frame luminance for multi-picture and the threshold SL for S/N adaptation. Bits D7-D5: Frame Luminance YF 0 black : : : : : : 7 white Bits D4-D0: Threshold SL (S/N adaptation) 0 ...

Page 7

Register R3: This register is for testing. certain S/N classes and filter coefficients for the motion detector can be firmly set. Bits D7-D5: S/N Class Automatic adaptation Class 0 Class 1 Class 2 Bits D4-D0: Filter Coefficient Motion detector ON ...

Page 8

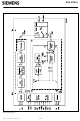

Block Diagram Semiconductor Group 266 SDA 9290-5 ...

Page 9

Pin Configuration (top view) Semiconductor Group 267 SDA 9290-5 ...

Page 10

Pin Definitions and Functions Pin Symbol Function No Positive supply DD voltage (+ 5 V) 2-9 UVQ7 … Data outputs UVQ0 V 10 Ground SS 11-18 UVB0 … Back-channel data UVB7 outputs 19-26 YB0 … Back- channel YB7 ...

Page 11

Pin Definitions and Functions (cont’d) Pin Symbol Function No SDA I C Bus data input/output 51 VS1 Vertical sync input (50 Hz Positive supply DD voltage (+ FSBQ Selection of output format 54 ...

Page 12

Characteristics (all voltages are referred to Parameter H-input voltage 1) L-input voltage 1) 1) Input current Input capacitance 1) (except BLN, LLIN) Input capacitance 1) (only BLN, LLIN) H-input voltage 2) L-input voltage 2) Input capacitance 2) Input current 2) ...

Page 13

Characteristics (cont’d) (all voltages are referred to Parameter Input Clock LL3X = 13.5 MHz (refer to figure 3) Cycle Fall time Rise time H-pulse width L-pulse width Change in rel to LLIN Input Clock LLIN (refer to figure 3) Cycle ...

Page 14

Characteristics (cont’d) (all voltages are referred to Parameter Input Signal VS1 Setup time Hold time Cycle, 625 lines Cycle, 525 lines H-pulse width, 625 lines L-pulse width, 525 lines Input Signal DREQ Setup time Hold time H-pulse width Input Signal ...

Page 15

Figure 1 Application Circuit (simplified) Semiconductor Group 273 SDA 9290-5 ...

Page 16

Figure 2 Timing Diagram Semiconductor Group 274 SDA 9290-5 ...

Page 17

Figure 3 Timing Diagram Semiconductor Group 275 SDA 9290-5 ...

Page 18

Figure 4 2 Timing for I C Bus All values are referred to specified input levels Parameter Clock frequency Inactive time before start of new transmission Hold time for start condition (after this time first clock pulse is generated) Low ...

Page 19

Figure 5 Picture Formats for 9-Image Display Semiconductor Group 277 SDA 9290-5 ...

Page 20

Y:7-Bit Signal Y:8-Bit Signal – ...

Page 21

Signal UV7 UV6 UV5 UV4 UV3 UV2 UV1 UV0 Figure 7 Assignment of Signal and Pin Names Format 4:2:2 Semiconductor Group Picture Processor Input Back Channel Input YI7 YB7 YI6 YB6 YI5 ...

Page 22

Figure 8 Output Data Delay Times Semiconductor Group 280 SDA 9290-5 ...