M27C1001-12F1 STMicroelectronics, M27C1001-12F1 Datasheet - Page 9

M27C1001-12F1

Manufacturer Part Number

M27C1001-12F1

Description

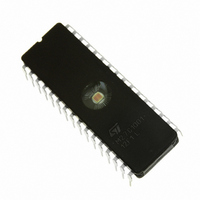

IC EPROM 1MBIT 120NS 32CDIP

Manufacturer

STMicroelectronics

Datasheets

1.M27C1001-12C6.pdf

(24 pages)

2.M27C1001-15F1.pdf

(10 pages)

3.M27C1001-12F1.pdf

(17 pages)

Specifications of M27C1001-12F1

Format - Memory

EPROMs

Memory Type

UV EPROM

Memory Size

1M (128K x 8)

Speed

120ns

Interface

Parallel

Voltage - Supply

4.5 V ~ 5.5 V

Operating Temperature

0°C ~ 70°C

Package / Case

32-CDIP (0.600", 15.24mm) Window

Capacitance, Input

6 pF

Capacitance, Output

12 pF

Current, Input, Leakage

±10 μA (Read)

Current, Operating

30 mA (Read)

Current, Output, Leakage

±10 μA (Read)

Current, Supply

30 mA

Density

1M

Organization

128K×8

Package Type

FDIP32W

Temperature, Operating

0 to +70 °C

Temperature, Operating, Maximum

70 °C

Temperature, Operating, Minimum

0 °C

Time, Access

120 ns

Time, Fall

≤20 ns

Time, Programmable

100 μs

Time, Rise

≤20 ns

Voltage, Input, High

6 V (Read)

Voltage, Input, High Level

2 V (Min.)

Voltage, Input, Low

0.8 V (Read)

Voltage, Input, Low Level

-0.3 V (Max.)

Voltage, Output, High

4.3 V (Read)

Voltage, Output, Low

0.4 V (Read)

Voltage, Programmable

11.5 V (Min.)

Voltage, Supply

5 V

Memory Configuration

128K X 8

Access Time

120ns

Supply Voltage Range

4.5V To 5.5V

Memory Case Style

DIP

No. Of Pins

32

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-1631-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M27C1001-12F1

Manufacturer:

ST

Quantity:

651

Part Number:

M27C1001-12F1

Manufacturer:

ST

Quantity:

20 000

Part Number:

M27C1001-12F1L

Manufacturer:

ST

Quantity:

20 000

M27C1001

2.4

2.5

2.6

ensures that all deselected memory devices are in their low power standby mode and that

the output pins are only active when data is required from a particular memory device.

System considerations

The power switching characteristics of Advanced CMOS EPROMs require careful

decoupling of the devices. The supply current, I

the system designer: the standby current level, the active current level, and transient current

peaks that are produced by the falling and rising edges of E. The magnitude of the transient

current peaks is dependent on the capacitive and inductive loading of the device at the

output. The associated transient voltage peaks can be suppressed by complying with the

two line output control and by properly selected decoupling capacitors. It is recommended

that a 0.1µF ceramic capacitor be used on every device between V

be a high frequency capacitor of low inherent inductance and should be placed as close to

the device as possible. In addition, a 4.7µF bulk electrolytic capacitor should be used

between V

power supply connection point. The purpose of the bulk capacitor is to overcome the voltage

drop caused by the inductive effects of PCB traces.

Programming

When delivered (and after each erasure for UV EPROM), all bits of the M27C1001 are in the

'1' state. Data is introduced by selectively programming '0's into the desired bit locations.

Although only '0's will be programmed, both '1's and '0's can be present in the data word.

The only way to change a '0' to a '1' is by die exposition to ultraviolet light (UV EPROM). The

M27C1001 is in the programming mode when V

pulsed to V

pins. The levels required for the address and data inputs are TTL. V

6.25V ± 0.25V.

Presto II programming algorithm

Presto II Programming Algorithm allows the whole array to be programmed, with a

guaranteed margin, in a typical time of 13 seconds. Programming with Presto II involves in

applying a sequence of 100µs program pulses to each byte until a correct verify occurs (see

Figure

activated in order to guarantee that each cell is programmed with enough margin. No

overprogram pulse is applied since the verify in Margin mode provides necessary margin to

each programmed cell.

5). During programming and verify operation, a Margin mode circuit is automatically

CC

IL

. The data to be programmed is applied to 8 bits in parallel to the data output

and V

SS

for every eight devices. The bulk capacitor should be located near the

CC

PP

, has three segments that are of interest to

input is at 12.75V, E is at V

CC

CC

and V

is specified to be

Device description

SS

IL

. This should

and P is

9/24