IR3503MTRPBF International Rectifier, IR3503MTRPBF Datasheet

IR3503MTRPBF

Specifications of IR3503MTRPBF

Related parts for IR3503MTRPBF

IR3503MTRPBF Summary of contents

Page 1

... Remote sense amplifier with true converter voltage sensing • Simplified VR Ready (VRRDY) output provides indication of proper operation • Small thermally enhanced 32L 5mm x 5mm MLPQ package • RoHS Compliant ORDERING INFORMATION Device IR3503MTRPBF * IR3503MPBF • Samples only Page XPHASE3 TM Phase IC provides a full featured and flexible way to Package ...

Page 2

APPLICATION CIRCUIT +12V PSI# VRRDY RMON IOUT RMON1 CMON CVCCL VOSEN- 33 EXPAD 1 VID7 VID7 2 VID6 VID6 3 VID5 VID5 4 VID4 VID4 5 VID3 VID3 6 VID2 VID2 7 VID1 VID1 8 VID0 VID0 ENABLE VRHOT RHOTSET1 ...

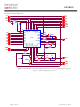

Page 3

IR3503 VDAC BUFFER AMPLIFIER + FAST ISOURCE VDAC ISINK - IVDAC CURRENT SOURCE IROSC GENERATOR Figure 2: System set-point measurements Page ERROR AMPLIFIER + - IVSETPT IROSC ROSC BUFFER AMPLIFIER 0. REMOTE SENSE AMPLIFIER + ...

Page 4

ABSOLUTE MAXIMUM RATINGS Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the ...

Page 5

ELECTRICAL SPECIFICATIONS Unless otherwise specified, these specifications apply over: 4.75 V<VCCL<7.5 V, -0.3 V ≤ VOSEN- ≤ 0 ≤ 100 C, 7.75 k ≤ R ≤ 50 OSC J PARAMETER VDAC Reference System ...

Page 6

PARAMETER Soft Start and Delay Start Delay (TD1) Soft Start Time (TD2) VID Sample Delay (TD3) VRRDY Delay (TD4 + TD5) OC Delay Time SS/DEL to FB Input Offset Voltage Charge/Discharge Current Ratio Charge Voltage Remote Sense Differential Amplifier Input ...

Page 7

PARAMETER Reduced Phase OC Threshold: Total number of phases ≤ 15 Over-Current Delay Counter Over-Current Delay Counter Over-Current Delay Counter Over Voltage Protection (OVP) Comparators Rising Threshold OVP Release Voltage Threshold during Dynamic VID down Dynamic VID Detect Comparator Threshold ...

Page 8

PIN DESCRIPTION PIN# PIN SYMBOL 1-8 VID7-0 Inputs to VID Converter. 9 ENABLE Enable input. A logic low applied to this pin puts the IC into fault mode. Do not float this pin as the logic state ...

Page 9

SYSTEM THEORY OF OPERATION Description: The system consists of one control IC and scalable number of phase IC’s depending upon the number of converter phases. The control IC communicates with the phase ICs using three digital buses, i.e., CLOCK, PHSIN, ...

Page 10

APPLICATION SYSTEM CIRCUIT +12V 4.75V to 7.5V VCCL PSI# VRRDY RMON IOUT RMON1 CMON CVCCL VOSEN- 33 EXPAD 1 24 VID7 VID7 PSI VID6 VID6 ROSC 3 22 VID5 VID5 SS/DEL 4 21 VID4 VID4 VDAC IR3503 5 ...

Page 11

During power up, the control IC sends out clock signals from both CLKOUT and PHSOUT pins and detects the feedback at PHSIN pin to determine the phase number and monitor any fault in the daisy chain loop. Figure 5 shows ...

Page 12

PWM Operation The PWM comparator is located in the phase IC. With the PHSIN voltage high, upon receiving the falling edge of a clock pulse, the PWM latch is set. The PWMRMP voltage begins to increase; the low side driver ...

Page 13

Since the voltage drop in the body diode is often comparable to the output voltage, the inductor current slew rate can be increased significantly. This patented technique is referred to as “body braking” and is accomplished through the “body braking ...

Page 14

Current Sense Amplifier A high speed differential current sense amplifier is located in the phase IC, as shown in Figure 7. Its gain is nominally 33 at 25ºC, and the 3850 ppm/ºC increase in inductor DCR should be compensated in ...

Page 15

Adaptive Voltage Positioning (AVP) Adaptive voltage positioning is needed to optimize the output voltage excursions during dynamic load variations. The objective of AVP is to control the output voltage to a value that is slightly higher than the minimum value ...

Page 16

Inductor DCR Temperature Compensation A negative temperature coefficient (NTC) thermistor should be used for inductor DCR temperature compensation. The thermistor and tuning resistor network connected between the VN and VDRP pins provides a single NTC thermal compensation. The thermistor should ...

Page 17

Block Diagram Page Figure 10: Block Diagram IR3503 February 12, 2010 ...

Page 18

TABLE 1: VR11 VID TABLE (PART1) Hex (VID7:VID0) Bin (VID7:VID0) 00 00000000 01 00000001 02 00000010 03 00000011 04 00000100 05 00000101 06 00000110 07 00000111 08 00001000 09 00001001 0A 00001010 0B 00001011 0C 00001100 0D 00001101 0E 00001110 ...

Page 19

TABLE 1: VR11 VID TABLE (PART 2) Hex (VID7:VID0) Bin (VID7:VID0) 80 10000000 81 10000001 82 10000010 83 10000011 84 10000100 85 10000101 86 10000110 87 10000111 88 10001000 89 10001001 8A 10001010 8B 10001011 8C 10001100 8D 10001101 8E ...

Page 20

Start-up Sequence The IR3503 has a programmable soft-start function to limit the surge current during the converter start-up. A capacitor connected between the SS/DEL and LGND pins controls soft start timing, over-current protection delay and hiccup mode timing. A charge ...

Page 21

RTCMP2 and RTCMP3. The IMON signal is clamped at 1.03V in order to facilitate direct interfacing with the CPU. VDAC Figure 12: Current Report Signal (IMON) implementation Power State ...

Page 22

V CCL 2 Figure 13 clearly explains the SHIFT functionality. The phase ICs wait for 8 PHSIN cycles after the assertion of PSI# to start shedding the phases (and issue a down SHIFT signal). When the phases are shed, the ...

Page 23

ICs and de-asserting the VRRDY signal. The output current is not controlled during the delay time. The SS/DEL capacitor will discharge until it reaches 200 mV and the fault latch is reset ...

Page 24

OUTPUT OVP VOLTAGE THRESHOLD (VO) VCCL-800 mV IIN (ISHARE) GATEH (PHASE IC) GATEL (PHASE IC) FAULT LATCH ERROR AMPLIFIER VDAC OUTPUT (EAOUT) Figure 15: Over voltage protection during normal operation During dynamic VID down, OVP may be triggered when output ...

Page 25

VID (FAST VDAC) VDAC OV THRESHOLD OUTPUT VOLTAGE (VO) NORMAL OPERATION Figure 16: Over voltage protection during dynamic VID transition VID Fault Codes VID codes of 0000000X and 1111111X for VR11 will set the fault latch and disable the error ...

Page 26

VDAC voltage change at light load with large output capacitance. Therefore, over-voltage threshold is raised to 1.73 V from VDAC+130 mV whenever dynamic VID is detected and the difference between output voltage and VDAC is more than 50mV, as shown ...

Page 27

Fault Operation Table Open Open Control Daisy Loop Fault Clearing Recycle VCCL Method Error Amp Disabled ROSC/OVP & IIN drive high until No OV clears SS/DEL Discharge Flags PGood 8 Delay 32 Clock PHSOUT Pulses Pulses Page ...

Page 28

DESIGN PROCEDURES - IR3503 AND IR3529 CHIPSET IR3503 EXTERNAL COMPONENTS Oscillator Resistor Rosc The oscillator of IR3503 generates square-wave pulses to synchronize the phase ICs. The switching frequency of the each phase converter equals the PHSOUT frequency, which is set ...

Page 29

C SS The soft start delay time (TD1) and VR ready delay time (TD3) are determined by (8) to (9) respectively Once C is chosen, the minimum over-current fault latch delay time SS/DEL t OCDEL VDAC Slew Rate ...

Page 30

RTHERM = C TH Droop Resistor The inductor DC resistance is utilized to sense the inductor current. The copper wire of inductor has a constant temperature coefficient of 3850 ppm/° C, and therefore the maximum inductor DCR can be calculated ...

Page 31

Thermistor R and Over Temperature Setting Resistors R THERM The threshold voltage of VRHOT comparator is fixed at 1.6V, and a negative temperature coefficient (NTC) thermistor R is required to sense the temperature of the power stage pre-select ...

Page 32

DESIGN EXAMPLE SPECIFICATIONS Input Voltage DAC Voltage 1.2 V DAC No Load Output Voltage Offset: V Continuous Output Current: I OTDC Current for Gain Setting for IMON: I Current Report Gain = 0.95 V ...

Page 33

VID rise time is − DEL DAC = = CHG The VRRDY delay time is − ...

Page 34

Droop Resistor Based on the above calculation R Pre-select and using find out R . DRP R DRP Over Current Threshold The OCP threshold is fixed at 1.17 V above the VDAC voltage. ...

Page 35

Layout Guidelines The following layout guidelines are recommended to reduce the parasitic inductance and resistance of the PCB layout, therefore minimizing the noise coupled to the IC. • Dedicate at least one middle layer for a ground plane LGND. • ...

Page 36

PCB Metal and Component Placement • Lead land width should be equal to nominal part lead width. The minimum lead to lead spacing should be ≥ 0.2mm to minimize shorting. • Lead land length should be equal to maximum part ...

Page 37

Solder Resist • The solder resist should be pulled away from the metal lead lands by a minimum of 0.06mm. The solder resist mis-alignment is a maximum of 0.05mm and it is recommended that the lead lands are all Non ...

Page 38

Stencil Design • The stencil apertures for the lead lands should be approximately 80% of the area of the lead lands. Reducing the amount of solder deposited will minimize the occurrence of lead shorts. Since for 0.5mm pitch devices the ...

Page 39

PACKAGE INFORMATION 32L MLPQ ( Body) – θ IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903Visit us at www.irf.com for sales contact information. www.irf.com Page 39 of ...