EVAL-AD5449EBZ Analog Devices Inc, EVAL-AD5449EBZ Datasheet - Page 21

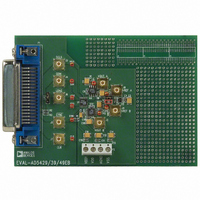

EVAL-AD5449EBZ

Manufacturer Part Number

EVAL-AD5449EBZ

Description

BOARD EVALUATION FOR AD5449

Manufacturer

Analog Devices Inc

Specifications of EVAL-AD5449EBZ

Number Of Dac's

2

Number Of Bits

12

Outputs And Type

2, Differential

Sampling Rate (per Second)

2.47M

Data Interface

Serial

Settling Time

80ns

Dac Type

Current

Voltage Supply Source

Single

Operating Temperature

-40°C ~ 125°C

Utilized Ic / Part

AD5449

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

SYNC Function

SYNC is an edge-triggered input that acts as a frame synchron-

ization signal and chip enable. Data can be transferred into the

device only while SYNC is low. To start the serial data transfer,

SYNC should be taken low, observing the minimum SYNC

falling edge to SCLK falling edge setup time, t

Daisy-Chain Mode

Daisy-chain mode is the default power-on mode. To disable the

daisy-chain function, write 1001 to the control word. In daisy-

chain mode, the internal gating on SCLK is disabled. SCLK is

continuously applied to the input shift register when SYNC is

low. If more than 16 clock pulses are applied, the data ripples

out of the shift register and appears on the SDO line. This data

is clocked out on the rising edge of SCLK (this is the default; use

the control word to change the active edge) and is valid for the

next device on the falling edge of SCLK (default). By connecting

this line to the SDIN input on the next device in the chain,

a multidevice interface is constructed. For each device in the

system, 16 clock pulses are required. Therefore, the total number

of clock cycles must equal 16 n, where n is the total number of

devices in the chain. See

When the serial transfer to all devices is complete, SYNC should

be taken high. This prevents additional data from being clocked

into the input shift register. A burst clock containing the exact

number of clock cycles can be used, after which SYNC can be

taken high. After the rising edge of SYNC , data is automatically

transferred from the input shift register of each device to the

addressed DAC.

Table 11. DAC Control Bits

C3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

C2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

1

0

1

1

0

1

C1

0

0

1

1

0

1

0

0

1

Figure 4

1

1

1

0

1

0

1

C0

0

1

0

1

0

0

0

1

0

.

B

A and B

N/A

N/A

N/A

N/A

N/A

DAC

A and B

A

A

A

B

B

A and B

N/A

N/A

4

.

Rev. C | Page 21 of 32

Function Implemented

No operation (power-on default)

Load and update

Initiate readback

Load input register

Load and update

Initiate readback

Load input register

Update DAC outputs

Load input registers

Disable daisy-chain

Clock data to shift register on rising edge

Clear DAC output to zero scale

Clear DAC output to midscale

Control word

Reserved

No operation

When control bits = 0000, the device is in no operation mode.

This may be useful in daisy-chain applications in which the user

does not want to change the settings of a particular DAC in the

chain. Write 0000 to the control bits for that DAC; subsequent

data bits are ignored.

Standalone Mode

After power-on, write 1001 to the control word to disable daisy-

chain mode. The first falling edge of SYNC resets the serial

clock counter to ensure that the correct number of bits are

shifted in and out of the serial shift registers. A SYNC edge

during the 16-bit write cycle causes the device to abort the

current write cycle.

After the falling edge of the 16th SCLK pulse, data is automat-

ically transferred from the input shift register to the DAC. For

another serial transfer to take place, the counter must be reset

by the falling edge of SYNC .

LDAC Function

The LDAC function allows asynchronous and synchronous

updates to the DAC output. The DAC is asynchronously updated

when this signal goes low. Alternatively, if this line is held perma-

nently low, an automatic or synchronous update mode is selected,

whereby the DAC is updated on the 16th clock falling edge when

the device is in standalone mode, or on the rising edge of SYNC

when the device is in daisy-chain mode.

Software LDAC Function

Load-and-update mode can also serve as a software update func-

tion, irrespective of the voltage level on the LDAC pin.

AD5429/AD5439/AD5449