EVAL-AD5391EBZ Analog Devices Inc, EVAL-AD5391EBZ Datasheet - Page 12

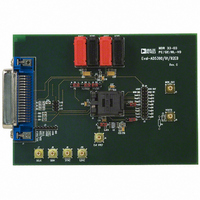

EVAL-AD5391EBZ

Manufacturer Part Number

EVAL-AD5391EBZ

Description

BOARD EVALUATION FOR AD5391

Manufacturer

Analog Devices Inc

Specifications of EVAL-AD5391EBZ

Number Of Dac's

16

Number Of Bits

12

Outputs And Type

16, Single Ended

Sampling Rate (per Second)

167k

Data Interface

Serial

Settling Time

6µs

Dac Type

Voltage

Voltage Supply Source

Single

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

AD5391

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

AD5390/AD5391/AD5392

I

DV

Table 7. I

Parameter

F

t

t

t

t

t

t

t

t

t

t

t

C

1

2

3

4

1

2

3

4

5

6

7

8

9

10

11

2

See Figure 6.

Guaranteed by design and characterization, not production tested.

A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the V

C

SCL

B

3

C SERIAL INTERFACE

B

4

is the total capacitance of one bus line in pF; t

DD

= 2.7 V to 5.5 V; AV

2

C Serial Interface

2

SDA

SCL

Limit at T

400

2.5

0.6

1.3

0.6

100

0.9

0

0.6

0.6

1.3

300

0

300

0

300

20 + 0.1 C

400

DD

= 2.7 V to 5.5 V; AGND = DGND = 0 V. All specifications T

1

t

9

MIN

B

CONDITION

, T

START

MAX

t

4

R

and t

t

3

F

measured between 0.3 DV

pF max

Unit

kHz max

μs min

μs min

μs min

μs min

ns min

μs max

μs min

μs min

μs min

μs min

ns max

ns min

ns max

ns min

ns max

ns min

t

10

t

6

Figure 6. I

t

11

Rev. C | Page 12 of 40

2

Description

SCL clock frequency

SCL cycle time

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

Capacitive load for each bus line

t

C Interface Timing Diagram

2

HIGH

LOW

HD

SU

HD

HD

SU

SU

BUF

F

R

F

F

F

F

, fall time of SDA when transmitting

, fall time of SDA when transmitting

, fall time of SDA when receiving (CMOS-compatible)

, fall time of SCL and SDA when receiving

, fall time of SCL and SDA when transmitting

, rise time of SCL and SDA when receiving (CMOS-compatible)

,

,

,

,

,

,

, bus free time between a stop and a start condition

DAT

STA

STO

, SCL low time

STA

DAT

DAT

, SCL high time

, start/repeated start condition hold time

, data setup time

setup time for repeated start

stop condition setup time

data hold time

data hold time

DD

and 0.7 DV

t

5

IH

MIN of the SCL signal) to bridge the undefined region of SCL’s falling edge.

DD

t

7

CONDITION

REPEATED

.

START

t

4

MIN

to T

t

1

MAX

, unless otherwise noted.

CONDITION

STOP

t

8