ATTINY24V-10MU Atmel, ATTINY24V-10MU Datasheet - Page 156

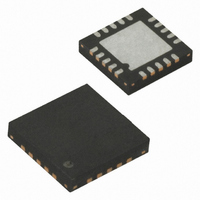

ATTINY24V-10MU

Manufacturer Part Number

ATTINY24V-10MU

Description

IC MCU AVR 2K FLASH 10MHZ 20-QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY24V-10MU

Core Processor

AVR

Core Size

8-Bit

Speed

10MHz

Connectivity

USI

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

12

Program Memory Size

2KB (1K x 16)

Program Memory Type

FLASH

Eeprom Size

128 x 8

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

20-MLF®, QFN

Cpu Family

ATtiny

Device Core

AVR

Device Core Size

8b

Frequency (max)

10MHz

Interface Type

SPI/USI

Total Internal Ram Size

128Byte

# I/os (max)

12

Number Of Timers - General Purpose

2

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

1.8V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

RISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

20

Package Type

MLF

Processor Series

ATTINY2x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

128 B

Maximum Clock Frequency

10 MHz

Number Of Programmable I/os

12

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

For Use With

ATSTK600-DIP40 - STK600 SOCKET/ADAPTER 40-PDIP770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAGATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK505 - ADAPTER KIT FOR 14PIN AVR MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATTINY24V-10MU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 156 of 238

- Download datasheet (5Mb)

18.6.3

156

ATtiny24/44/84

Reading Device Signature Imprint Table from Firmware

To read the Fuse High Byte (FHB), simply replace the address in the Z-pointer with 0x0003 and

repeat the procedure above. If successful, the contents of the destination register are as follows.

Refer to

To read the Fuse Extended Byte (FEB), replace the address in the Z-pointer with 0x0002 and

repeat the previous procedure. If successful, the contents of the destination register are as

follows.

Refer to

Byte.

To read the contents of the device signature imprint table, follow the below procedure:

The RSIG and SPMEN bits will auto-clear after three CPU cycles. When RSIG and SPMEN are

cleared, LPM will work as described in the “AVR Instruction Set” description.

See program example below.

Note:

Bit

Rd

Bit

Rd

Assembly Code Example

1. Load the Z-pointer with the table index.

2. Set RSIG and SPMEN bits in SPMCSR.

3. Issue an LPM instruction within three clock cycles.

4. Wait three clock cycles for SPMEN bits to be cleared.

5. Read table data from the LPM destination register.

DSIT_read:

; Uses Z-pointer as table index

ldi

ldi

; Preload SPMCSR bits into R16, then write to SPMCSR

ldi

out SPMCSR, r16

; Issue LPM. Table data will be returned into r17

lpm r17, Z

ret

See

Table 19-4 on page 160

Table 19-3 on page 160

“Code Examples” on page

ZH, 0

ZL, 1

r16, (1<<RSIG)|(1<<SPMEN)

FHB7

FEB7

7

7

FHB6

FEB6

6

6

for detailed description and mapping of the Fuse High Byte.

FHB5

FEB5

for detailed description and mapping of the Fuse Extended

5

5

6.

FHB4

FEB4

4

4

FHB3

FEB3

3

3

FHB2

FEB2

2

2

FHB1

FEB1

1

1

FHB0

FEB0

0

0

8006K–AVR–10/10

Related parts for ATTINY24V-10MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC MCU AVR 2K FLASH 10MHZ 14SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 2K FLASH 10MHZ 14-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 2KB FLASH 10MHZ 14SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 2KB FLASH 10MHZ 20QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

8-bit Avr Microcontroller With 2/4/8k Bytes Insystem Programmable Flash

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Microcontrollers - MCU Microcontroller

Manufacturer:

Atmel

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC MCU AVR 2K FLASH 20MHZ 20-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 2K FLASH 20MHZ 14SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 2K FLASH 15MHZ 20-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 2K FLASH 20MHZ 14-DIP

Manufacturer:

Atmel

Datasheet: