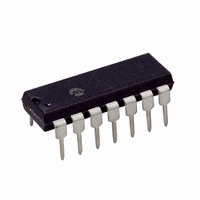

PIC16F610-I/P Microchip Technology, PIC16F610-I/P Datasheet

PIC16F610-I/P

Specifications of PIC16F610-I/P

Available stocks

Related parts for PIC16F610-I/P

PIC16F610-I/P Summary of contents

Page 1

... Microchip Technology Inc. PIC16F610/16HV610 PIC16F616/16HV616 Data Sheet 14-Pin, Flash-Based 8-Bit CMOS Microcontrollers Preliminary DS41288C ...

Page 2

... Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. ...

Page 3

... Precision Internal Oscillator: - Factory calibrated to ±1%, typical - User selectable frequency: 4 MHz or 8 MHz • Power-Saving Sleep mode • Voltage range: - PIC16F610/616: 2.0V to 5.5V - PIC16HV610/616: 2.0V to user defined maximum (see note) • Industrial and Extended Temperature range • Power-on Reset (POR) • ...

Page 4

... PIC16F610/616/16HV610/616 Program Memory Data Memory Device Flash SRAM (bytes) (words) PIC16F610 1024 PIC16HV610 1024 PIC16F616 2048 PIC16HV616 2048 PIC16F610/16HV610 14-Pin Diagram (PDIP, SOIC, TSSOP RA5/T1CKI/OSC1/CLKIN RA4/T1G/OSC2/CLKOUT RA3/MCLR/V PP RC5 RC4/C2OUT RC3/C12IN3- TABLE 1: PIC16F610/16HV610 I/O Pin Comparators RA0 13 C1IN+ RA1 12 C12IN0- RA2 11 C1OUT ...

Page 5

... AN7 C12IN3- RC4 6 — C2OUT RC5 5 — — — 1 — — — 14 — — Note 1: Input only. 2: Only when pin is configured for external MCLR. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 RA0/AN0/C1IN+/ICSPDAT 2 13 RA1/AN1/C12IN0-/ RA2/AN2/T0CKI/INT/C1OUT 4 10 RC0/AN4/C2IN RC1/AN5/C12IN1 RC2/AN6/C12IN2-/P1D 14- ...

Page 6

... PIC16F610/616/16HV610/616 PIC16F610/16HV610 16-Pin Diagram (QFN) RA5/T1CKI/OSC1/CLKIN RA4/T1G/OSC2/CLKOUT RA3/MCLR/V PP RC5 TABLE 3: PIC16F610/16HV610 I/O Pin Comparators RA0 12 C1IN+ RA1 11 C12IN0- RA2 10 C1OUT (1) RA3 3 — RA4 2 — RA5 1 — RC0 9 C2IN+ RC1 8 C12IN1- RC2 7 C12IN2- RC3 6 C12IN3- RC4 5 C2OUT RC5 4 — — 16 — — ...

Page 7

... C2OUT RC5 4 — — — 16 — — — 13 — — Note 1: Input only. 2: Only when pin is configured for external MCLR. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 RA0/AN0/C1IN+/ICSPDAT 12 1 RA1/AN1/C12IN0-/ PIC16F616/ PIC16HV616 RA2/AN2/T0CKI/INT/C1OUT 10 3 RC0/AN4/C2IN1 16- PIN SUMMARY Timers CCP Interrupts Pull-ups — ...

Page 8

... PIC16F610/616/16HV610/616 Table of Contents 1.0 Device Overview .......................................................................................................................................................................... 7 2.0 Memory Organization ................................................................................................................................................................. 11 3.0 Oscillator Module........................................................................................................................................................................ 25 4.0 I/O Ports ..................................................................................................................................................................................... 31 5.0 Timer0 Module ........................................................................................................................................................................... 43 6.0 Timer1 Module with Gate Control............................................................................................................................................... 47 7.0 Timer2 Module ........................................................................................................................................................................... 53 8.0 Comparator Module.................................................................................................................................................................... 55 9.0 Analog-to-Digital Converter (ADC) Module ................................................................................................................................ 71 10.0 Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module ................................................................. 83 11 ...

Page 9

... DEVICE OVERVIEW The PIC16F610/616/16HV610/616 is covered by this data sheet available in 14-pin PDIP, SOIC, TSSOP and 16-pin QFN packages. Block Diagrams and pinout descriptions of the devices are as follows: • PIC16F610/16HV610 (Figure 1-1, Table 1-1) • PIC16F616/16HV616 (Figure 1-2, Table 1-2) FIGURE 1-1: ...

Page 10

... PIC16F610/616/16HV610/616 FIGURE 1-2: PIC16F616/16HV616 BLOCK DIAGRAM Configuration Flash Program Memory Program 14 Bus Instruction Reg 8 Instruction Decode and Control Timing OSC1/CLKIN Generation OSC2/CLKOUT Internal Oscillator Block T1G T1CKI Timer0 T0CKI Analog-To-Digital Converter DS41288C-page 8 INT 13 Data Bus Program Counter RAM 8-Level Stack 128 Bytes ...

Page 11

... TABLE 1-1: PIC16F610/16HV610 PINOUT DESCRIPTION Name Function RA0/C1IN+/ICSPDAT RA1/C12IN0-/ICSPCLK RA2/T0CKI/INT/C1OUT RA3/MCLR/V PP RA4/T1G/OSC2/CLKOUT RA5/T1CKI/OSC1/CLKIN RC0/C2IN+ RC1/C12IN1- RC2/C12IN2- RC3/C12IN3- RC4/C2OUT RC5 Legend Analog input or output ST = Schmitt Trigger input with CMOS levels TTL © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Input Output Type ...

Page 12

... PIC16F610/616/16HV610/616 TABLE 1-2: PIC16F616/16HV616 PINOUT DESCRIPTION Name Function RA0/AN0/C1IN+/ICSPDAT RA1/AN1/C12IN0-/V /ICSPCLK REF RA2/AN2/T0CKI/INT/C1OUT RA3/MCLR/V PP RA4/AN3/T1G/OSC2/CLKOUT RA5/T1CKI/OSC1/CLKIN RC0/AN4/C2IN+ RC1/AN5/C12IN1- RC2/AN6/C12IN2-/P1D RC3/AN7/C12IN3-/P1C RC4/C2OUT/P1B RC5/CCP1/P1A Legend Analog input or output ST = Schmitt Trigger input with CMOS levels TTL DS41288C-page 10 Input Output Type Type ...

Page 13

... PIC16F610/16HV610 and the first (0000h-07FFh) for the PIC16F616/16HV616 is physically implemented. Accessing a location above these boundaries will cause a wraparound within the first space (PIC16F610/16HV610) and space (PIC16F616/16HV616). The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1). ...

Page 14

... Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of PIC16F610/16HV610 Register locations 40h-7Fh in Bank 0 are General Purpose Registers, implemented as static RAM. PIC16F616/16HV616 locations 20h-7Fh in Bank 0 and A0h-BFh in Bank 1 are General Purpose Registers, implemented as static RAM ...

Page 15

... FIGURE 2-3: DATA MEMORY MAP OF THE PIC16F610/16HV610 File Address (1) Indirect Addr. Indirect Addr. 00h OPTION_REG TMR0 01h PCL 02h PCL STATUS STATUS 03h FSR FSR 04h PORTA TRISA 05h 06h PORTC TRISC 07h 08h 09h PCLATH PCLATH 0Ah INTCON INTCON 0Bh ...

Page 16

... PIC16F610/616/16HV610/616 TABLE 2-1: PIC16F610/616/16HV610/616 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0 Addr Name Bit 7 Bit 6 Bank 0 00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 01h TMR0 Timer0 Module’s Register 02h PCL Program Counter’s (PC) Least Significant Byte ...

Page 17

... TABLE 2-2: PIC16F610/616/16HV610/616 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1 Addr Name Bit 7 Bit 6 Bank 1 80h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 81h OPTION_REG RAPU INTEDG 82h PCL Program Counter’s (PC) Least Significant Byte (1) (1) 83h ...

Page 18

... Status bits, see the Section 13.0 “Instruction Set Summary”. Note 1: Bits IRP and RP1 of the STATUS register are not PIC16F610/616/16HV610/616 should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products. 2: The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction ...

Page 19

... Microchip Technology Inc. PIC16F610/616/16HV610/616 Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit to ‘1’ of the OPTION register. See Section 5.1.3 “Software Programmable Prescaler”. R/W-1 ...

Page 20

... PIC16F610/616/16HV610/616 2.2.2.3 INTCON Register The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts. REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER R/W-0 R/W-0 R/W-0 GIE ...

Page 21

... TMR1IE: Timer1 Overflow Interrupt Enable bit 1 = Enables the Timer1 overflow interrupt 0 = Disables the Timer1 overflow interrupt Note 1: PIC16F616/16HV616 only. PIC16F610/16HV610 unimplemented, read as ‘0’. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt. ...

Page 22

... TMR1IF: Timer1 Overflow Interrupt Flag bit 1 = Timer1 register overflowed (must be cleared in software Timer1 has not overflowed Note 1: PIC16F616/16HV616 only. PIC16F610/16HV610 unimplemented, read as ‘0’. DS41288C-page 20 Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register ...

Page 23

... BOR: Brown-out Reset Status bit Brown-out Reset occurred Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) Note 1: Reads as ‘0’ if Brown-out Reset is disabled. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 U-0 U-0 U-0 — — — Unimplemented bit, read as ‘0’ ...

Page 24

... Table Read” (DS00556). DS41288C-page 22 2.3.2 STACK The PIC16F610/616/16HV610/616 Family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch ...

Page 25

... FIGURE 2-6: DIRECT/INDIRECT ADDRESSING PIC16F610/16HV610 Direct Addressing (1) From Opcode RP1 RP0 6 Bank Select Location Select 00h Data 20h Memory 40h 70h 7Fh Bank 0 For memory map detail, see Figure 2-3. Unimplemented data memory locations, read as ‘0’. Note 1: The RP1 and IRP bits are reserved; always maintain these bits clear. ...

Page 26

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 24 Preliminary © 2007 Microchip Technology Inc. ...

Page 27

... External Oscillator OSC2 Sleep OSC1 Internal Oscillator INTOSC 8 MHz © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 The Oscillator module can be configured in one of eight clock modes – External clock with I/O on OSC2/CLKOUT – 32 kHz Low-Power Crystal mode – Medium Gain Crystal or Ceramic Resonator Oscillator mode ...

Page 28

... PIC16F610/616/16HV610/616 3.2 Clock Source Modes Clock Source modes can be classified as external or internal. • External Clock modes rely on external circuitry for the clock source. Examples are: Oscillator mod- ules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits. ...

Page 29

... The value of R varies with the Oscillator mode F selected (typically between 2 MΩ MΩ). © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application ...

Page 30

... PIC16F610/616/16HV610/616 3.3.4 EXTERNAL RC MODES The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4 ...

Page 31

... Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation. 2: See Configuration Word register (Register 12-1) for operation of all register bits. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 The default value of the OSCTUNE register is ‘0’. The value is a 5-bit two’s complement number. When the OSCTUNE register is modified, the frequency will begin shifting to the new frequency ...

Page 32

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 30 Preliminary © 2007 Microchip Technology Inc. ...

Page 33

... TRISA<3> always reads ‘1’. 2: TRISA<5:4> always reads ‘1’ in XT, HS and LP Oscillator modes. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 port pins are read, this value is modified and then written to the PORT data latch. RA3 reads ‘0’ when MCLRE = 1. The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs ...

Page 34

... PIC16F610/616/16HV610/616 4.2 Additional Pin Functions Every PORTA pin on the PIC16F610/616/16HV610/ 616 has an interrupt-on-change option and a weak pull- up option. The next three sections describe these functions. 4.2.1 ANSEL REGISTER The ANSEL register is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as ‘ ...

Page 35

... Interrupt-on-change enabled 0 = Interrupt-on-change disabled Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized. 2: IOCA<5:4> always reads ‘1’ in XT, HS and LP Oscillator modes. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 R/W-1 U-0 R/W-1 WPUA4 — WPUA2 U = Unimplemented bit, read as ‘0’ ...

Page 36

... PIC16F610/616/16HV610/616 4.2.4 PIN DESCRIPTIONS AND DIAGRAMS Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet. ...

Page 37

... IOAC RD IOAC ( Interrupt-on- From other Change R RA<5:3, 1:0> pins Write ‘0’ to RAIF Note 1: Comparator mode and ANSEL determines Analog Input mode. 2: Set has priority over Reset. 3: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Analog Input Mode C1OE Enable C1OE ...

Page 38

... PIC16F610/616/16HV610/616 4.2.4.4 RA3/MCLR/V PP Figure 4-3 shows the diagram for this pin. The RA3 pin is configurable to function as one of the following: • a general purpose input • as Master Clear Reset with weak pull-up FIGURE 4-3: BLOCK DIAGRAM OF RA3 Data Bus RD TRISA RD PORTA WR IOCA RD IOCA ...

Page 39

... Note 1: CLK modes are XT, HS, LP, TMR1 LP and CLKOUT Enable. 2: With CLKOUT option. 3: Analog Input mode comes from ANSEL. 4: Set has priority over Reset. 5: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 • a Timer1 gate (count enable) • a crystal/resonator connection • a clock output Note 1: PIC16F616/16HV616 only. Analog ...

Page 40

... PIC16F610/616/16HV610/616 4.2.4.6 RA5/T1CKI/OSC1/CLKIN Figure 4-5 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following: FIGURE 4-5: BLOCK DIAGRAM OF RA5 ( Interrupt-on- Change R Write ‘0’ to RAIF Note 1: Timer1 LP Oscillator enabled. 2: Set has priority over Reset. DS41288C-page 38 • a general purpose I/O • ...

Page 41

... RA5 TRISA — — TRISA5 WPUA — — WPUA5 Legend unknown unchanged, – = unimplemented locations read as ‘0’. Shaded cells are not used by PORTA. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Bit 4 Bit 3 Bit 2 Bit 1 ANS4 ANS3 ANS2 ANS1 — C1POL C1R ...

Page 42

... PIC16F610/616/16HV610/616 4.3 PORTC and the TRISC Registers PORTC is a general purpose I/O port consisting of 6 bidirectional pins. The pins can be configured for either digital I/O or analog input to A/D Converter (ADC) or Comparator. For specific information about individual functions such as the Enhanced CCP or the ADC, refer to the appropriate section in this data sheet ...

Page 43

... PORTC To Comparators To A/D Converter Note 1: Analog Input mode comes from ANSEL or Comparator mode. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 4.3.3 RC2/AN6 The RC2 is configurable to function as one of the following: • a general purpose I/O • an analog input for the ADC • an analog input to Comparators C1 and C2 • ...

Page 44

... PIC16F610/616/16HV610/616 (1) 4.3.5 RC4/C2OUT/P1B The RC4 is configurable to function as one of the following: • a general purpose I/O • a digital output from Comparator C2 • a digital output from the Enhanced CCP Note 1: PIC16F616/16HV616 only. 2: Enabling both C2OUT and P1B will cause a conflict on RC4 and create unpredictable results ...

Page 45

... Timer Note 1: T0SE, T0CS, PSA, PS<2:0> are bits in the OPTION register. 2: WDTE bit is in the Configuration Word register. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 5.1 Timer0 Operation When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter. ...

Page 46

... PIC16F610/616/16HV610/616 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a ‘0’. ...

Page 47

... TRISA5 TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 --11 1111 --11 1111 Legend: – = Unimplemented locations, read as ‘0’ unchanged unknown. Shaded cells are not used by the Timer0 module. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 R/W-1 R/W-1 R/W-1 T0SE PSA U = Unimplemented bit, read as ‘0’ ...

Page 48

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 46 Preliminary © 2007 Microchip Technology Inc. ...

Page 49

... ST Buffer is low power type when using LP osc, or high speed type when using T1CKI. 2: Timer1 register increments on rising edge. 3: Synchronize does not operate while in Sleep. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 6.1 Timer1 Operation The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter ...

Page 50

... PIC16F610/616/16HV610/616 6.2.1 INTERNAL CLOCK SOURCE When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples determined by the Timer1 prescaler. CY 6.2.2 EXTERNAL CLOCK SOURCE When the external clock source is selected, the Timer1 module may work as a timer or a counter. ...

Page 51

... Note 1: Arrows indicate counter increments Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event. ...

Page 52

... PIC16F610/616/16HV610/616 6.12 Timer1 Control Register The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module. REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER R/W-0 R/W-0 R/W-0 (1) (2) T1GINV TMR1GE T1CKPS1 bit 7 Legend Readable bit ...

Page 53

... Holding Register for the Least Significant Byte of the 16-bit TMR1 Register T1CON T1GINV TMR1GE T1CKPS1 Legend unknown unchanged, – = unimplemented, read as ‘0’. Shaded cells are not used by the Timer1 module. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Bit 4 Bit 3 Bit 2 Bit 1 C2POL — C2R C2CH1 T1ACS C1HYS ...

Page 54

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 52 Preliminary © 2007 Microchip Technology Inc. ...

Page 55

... T2CKPS<1:0> © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh. Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a ‘ ...

Page 56

... PIC16F610/616/16HV610/616 REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER U-0 R/W-0 R/W-0 — TOUTPS3 TOUTPS2 bit 7 Legend Readable bit W = Writable bit -n = Value at POR ‘1’ = Bit is set bit 7 Unimplemented: Read as ‘0’ bit 6-3 TOUTPS<3:0>: Timer2 Output Postscaler Select bits 0000 = 1:1 Postscaler ...

Page 57

... When the analog voltage at V less than the analog voltage the output of the IN comparator is a digital low level. When the analog voltage greater than the analog voltage the output of the comparator is a digital high level. IN © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 FIGURE 8- ...

Page 58

... PIC16F610/616/16HV610/616 FIGURE 8-2: COMPARATOR C1 SIMPLIFIED BLOCK DIAGRAM C1CH<1:0> 2 C12IN0- 0 C12IN1- 1 MUX C12IN2- 2 C12IN3- 3 C1R C1IN+ 0 MUX C1V REF 1 Note 1: When C1ON = 0, the C1 comparator will produce a ‘0’ output to the XOR Gate. 2: Output shown for reference only. See I/O port pin block diagram for more detail. ...

Page 59

... See Section 8.11 “Comparator Voltage Reference” for more information on the internal voltage reference module. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 8.2.4 COMPARATOR OUTPUT SELECTION The output of the comparator can be monitored by control ...

Page 60

... PIC16F610/616/16HV610/616 8.4 Comparator Interrupt Operation The comparator interrupt flag can be set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusive-or gate (see Figure 8-2 and Figure 8-3). One latch is updated with the comparator output level when the CMxCON0 register is read ...

Page 61

... INTCON register is also set, the device will then execute the interrupt service routine. 8.6 Effects of a Reset A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their OFF states. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Preliminary DS41288C-page 59 ...

Page 62

... PIC16F610/616/16HV610/616 REGISTER 8-1: CM1CON0: COMPARATOR 1 CONTROL REGISTER 0 R/W-0 R-0 R/W-0 C1ON C1OUT C1OE bit 7 Legend Readable bit W = Writable bit -n = Value at POR ‘1’ = Bit is set bit 7 C1ON: Comparator C1 Enable bit 1 = Comparator C1 is enabled 0 = Comparator C1 is disabled bit 6 C1OUT: Comparator C1 Output bit ...

Page 63

... C2 connects to C12IN2 C2V - pin of C2 connects to C12IN3- IN Note 1: Comparator output requires the following three conditions: C2OE = 1, C2ON = 1 and corresponding port TRIS bit = 0. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 R/W-0 U-0 C2POL — Unimplemented bit, read as ‘0’ ‘0’ = Bit is cleared + > C2V - ...

Page 64

... PIC16F610/616/16HV610/616 8.7 Comparator Analog Input Connection Considerations A simplified circuit for an analog input is shown in Figure 8-6. Since the analog input pins share their con- nection with a digital input, they have reverse biased ESD protection diodes to V and V DD input, therefore, must be between V ...

Page 65

... Timer1 gate source is SYNCC2OUT. bit 0 C2SYNC: Comparator C2 Output Synchronization bit Output is synchronous to falling edge of Timer1 clock Output is asynchronous © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 8.8.2 SYNCHRONIZING COMPARATOR C2 OUTPUT TO TIMER1 The Comparator C2 output can be synchronized with Timer1 by setting the C2SYNC bit of the CM2CON1 register ...

Page 66

... PIC16F610/616/16HV610/616 8.9 Comparator Hysteresis Each comparator has built-in hysteresis that is user enabled by setting the C1HYS or C2HYS bits of the CM2CON1 register. The hysteresis feature can help filter noise and reduce multiple comparator output transitions when the output is changing state. FIGURE 8-7: COMPARATOR HYSTERESIS ...

Page 67

... TRISC TRISC5 VRCON C1VREN C2VREN VRR Legend unknown unchanged, – = unimplemented, read as ‘0’. Shaded cells are not used for comparator. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Bit 4 Bit 3 Bit 2 Bit 1 ANS4 ANS3 ANS2 ANS1 C1POL C1SP C1R ...

Page 68

... PIC16F610/616/16HV610/616 8.10 Comparator SR Latch The SR latch module provides additional control of the comparator outputs. The module consists of a single SR latch and output multiplexers. The SR latch can be set, reset or toggled by the comparator outputs. The SR latch may also be set or reset, independent of comparator output, by control bits in the SRCON0 control register ...

Page 69

... F /16 OSC /32 OSC /64 OSC /128 OSC bit 5-0 Unimplemented: Read as ‘0’ © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 R/W-0 R/S-0 R/S-0 C2REN PULSS PULSR S = Bit is set only - U = Unimplemented bit, read as ‘0’ ‘0’ = Bit is cleared (2) (2) U-0 U-0 U-0 — ...

Page 70

... PIC16F610/616/16HV610/616 8.11 Comparator Voltage Reference The comparator voltage reference module provides an internally generated voltage reference for the compara- tors. The following features are available: • Independent from Comparator operation • Two 16-level voltage ranges • Output clamped • Ratiometric with V DD • ...

Page 71

... ADC Module C1VREN C2VREN To ADC Module Fixed Ref To Comparators and ADC Module © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 8.11.7 VOLTAGE REFERENCE SELECTION , with DD Multiplexers on the output of the voltage reference module enable selection of either the CV voltage reference for use by the comparators. ...

Page 72

... PIC16F610/616/16HV610/616 REGISTER 8-6: VRCON: VOLTAGE REFERENCE CONTROL REGISTER R/W-0 R/W-0 R/W-0 C1VREN C2VREN VRR bit 7 Legend Readable bit W = Writable bit -n = Value at POR ‘1’ = Bit is set bit 7 C1VREN: Comparator 1 Voltage Reference Enable bit circuit powered on and routed to C1V REF 0 = 0.6 Volt constant reference routed to C1V ...

Page 73

... Figure 9-1 shows the block diagram of the ADC. FIGURE 9-1: ADC BLOCK DIAGRAM RA0/AN0 RA1/AN1/V REF RA2/AN2 RA4/AN3 RC0/AN4 RC1/AN5 RC2/AN6 RC3/AN7 CV REF 0.6V Reference 1.2V Reference CHS <3:0> © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 (ADC) allows V DD VCFG = 0 V VCFG = 1 REF ADC GO/DONE ADFM ADON Preliminary 10 ...

Page 74

... PIC16F610/616/16HV610/616 9.1 ADC Configuration When configuring and using the ADC, the following functions must be considered: • Port configuration • Channel selection • ADC voltage reference selection • ADC conversion clock source • Interrupt control • Results formatting 9.1.1 PORT CONFIGURATION The ADC can be used to convert both analog and digital signals ...

Page 75

... Please see Section 9.1.5 “Interrupts” for more information. FIGURE 9-3: 10-BIT A/D CONVERSION RESULT FORMAT (ADFM = 0) MSB bit 7 (ADFM = 1) bit 7 Unimplemented: Read as ‘0’ © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 CYCLES ...

Page 76

... PIC16F610/616/16HV610/616 9.2 ADC Operation 9.2.1 STARTING A CONVERSION To enable the ADC module, the ADON bit of the ADCON0 register must be set to a ‘1’. Setting the GO/ DONE bit of the ADCON0 register to a ‘1’ will start the analog-to-digital conversion. Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 “ ...

Page 77

... BTFSC ADCON0,GO ;Is conversion done? GOTO $-1 ;No, test again BANKSEL ADRESH ; MOVF ADRESH,W ;Read upper 2 bits MOVWF RESULTHI ;store in GPR space BANKSEL ADRESL ; MOVF ADRESL,W ;Read lower 8 bits MOVWF RESULTLO ;Store in GPR space © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Preliminary DS41288C-page 75 ...

Page 78

... PIC16F610/616/16HV610/616 9.2.7 ADC REGISTER DEFINITIONS The following registers are used to control the operation of the ADC. REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0 R/W-0 R/W-0 R/W-0 ADFM VCFG CHS3 bit 7 Legend Readable bit W = Writable bit -n = Value at POR ‘1’ = Bit is set bit 7 ADFM: A/D Conversion Result Format Select bit ...

Page 79

... RC 100 = F /4 OSC 101 = F /16 OSC 110 = F /64 OSC bit 3-0 Unimplemented: Read as ‘0’ © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 R/W-0 U-0 U-0 ADCS0 — — Unimplemented bit, read as ‘0’ ‘0’ = Bit is cleared Preliminary U-0 U-0 — — ...

Page 80

... PIC16F610/616/16HV610/616 REGISTER 9-3: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0 (READ-ONLY) R-x R-x R-x ADRES9 ADRES8 ADRES7 bit 7 Legend Readable bit W = Writable bit -n = Value at POR ‘1’ = Bit is set bit 7-0 ADRES<9:2>: ADC Result Register bits Upper 8 bits of 10-bit conversion result ...

Page 81

... S Note 1: The reference voltage (V REF 2: The charge holding capacitor (C 3: The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 ) SS ) impedance SS = 50°C and external impedance of 10k + ...

Page 82

... PIC16F610/616/16HV610/616 FIGURE 9-4: ANALOG INPUT MODEL ANx Rs C PIN Legend Input Capacitance PIN V = Threshold Voltage Leakage current at the pin due to LEAKAGE various junctions R = Interconnect Resistance Sampling Switch C = Sample/Hold Capacitance HOLD FIGURE 9-5: ADC TRANSFER FUNCTION 3FFh 3FEh 3FDh 3FCh 3FBh 004h ...

Page 83

... TRISA5 TRISC — — TRISC5 Legend unknown unchanged, – = unimplemented read as ‘0’. Shaded cells are not used for ADC module. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Bit 4 Bit 3 Bit 2 Bit 1 CHS2 CHS1 CHS0 GO/DONE ADCS0 — — ...

Page 84

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 82 Preliminary © 2007 Microchip Technology Inc. ...

Page 85

... PWM mode; P1A, P1C active-low; P1B, P1D active-high 1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle. ...

Page 86

... PIC16F610/616/16HV610/616 10.1 Capture Mode In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register: • Every falling edge • Every rising edge • Every 4th rising edge • ...

Page 87

... TRISC — — TRISC5 Legend: – = Unimplemented locations, read as ‘0’ unchanged unknown. Shaded cells are not used by the Capture, Compare and PWM. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Bit 4 Bit 3 Bit 2 Bit 1 DC1B0 CCP1M3 CCP1M2 CCP1M1 INTE ...

Page 88

... PIC16F610/616/16HV610/616 10.2 Compare Mode In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 module may: • Toggle the CCP1 output • Set the CCP1 output • Clear the CCP1 output • ...

Page 89

... TRISC — — TRISC5 Legend: – = Unimplemented locations, read as ‘0’ unchanged unknown. Shaded cells are not used by the Capture, Compare and PWM. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Bit 4 Bit 3 Bit 2 Bit 1 DC1B0 CCP1M3 CCP1M2 CCP1M1 INTE ...

Page 90

... PIC16F610/616/16HV610/616 10.3 PWM Mode The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers: • PR2 • T2CON • CCPR1L • CCP1CON In Pulse-Width Modulation (PWM) mode, the CCP module produces 10-bit resolution PWM output on the CCP1 pin ...

Page 91

... Timer Prescale (1, 4, 16) 16 PR2 Value 0x65 Maximum Resolution (bits) 8 © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 EQUATION 10-2: Pulse Width EQUATION 10-3: • OSC Duty Cycle Ratio The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation ...

Page 92

... PIC16F610/616/16HV610/616 10.3.4 OPERATION IN SLEEP MODE In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state. ...

Page 93

... Full-Bridge, Forward 01 Full-Bridge, Reverse 11 © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately. ...

Page 94

... PIC16F610/616/16HV610/616 FIGURE 10-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE) Signal P1M<1:0> P1A Modulated (Single Output) 00 P1A Modulated (Half-Bridge) 10 P1B Modulated P1A Active P1B Inactive (Full-Bridge, 01 Forward) P1C Inactive P1D Modulated P1A Inactive P1B Modulated (Full-Bridge, 11 Reverse) P1C Active P1D Inactive Relationships: • ...

Page 95

... Pulse Width = T * (CCPR1L<7:0>:CCP1CON<5:4>) * (TMR2 Prescale Value) OSC • Delay = (PWM1CON<6:0>) OSC Note 1: Dead-band delay is programmed using the PWM1CON register (Section 10.4.6 “Programmable Dead-Band Delay mode”). © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Pulse 0 Width Period (1) (1) Delay Delay Preliminary ...

Page 96

... PIC16F610/616/16HV610/616 10.4.1 HALF-BRIDGE MODE In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 10-8). This mode can be used for half-bridge applications, as ...

Page 97

... PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs. FIGURE 10-10: EXAMPLE OF FULL-BRIDGE APPLICATION P1A P1B P1C P1D © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 V+ QA FET Driver Load FET Driver QB V- ...

Page 98

... PIC16F610/616/16HV610/616 FIGURE 10-11: EXAMPLE OF FULL-BRIDGE PWM OUTPUT Forward Mode (2) P1A Pulse Width (2) P1B (2) P1C (2) P1D (1) Reverse Mode Pulse Width (2) P1A (2) P1B (2) P1C (2) P1D (1) Note 1: At this time, the TMR2 register is equal to the PR2 register. 2: Output signal is shown as active-high. DS41288C-page 96 Period (1) Period ...

Page 99

... When changing directions, the P1A and P1C signals switch before the end of the current PWM cycle. The modulated P1B and P1D signals are inactive at this time. The length of this time is four Timer2 counts. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required ...

Page 100

... PIC16F610/616/16HV610/616 FIGURE 10-13: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE P1A P1B P1C P1D External Switch C External Switch D Potential Shoot-Through Current Note 1: All signals are shown as active-high the turn on delay of power switch QC and its driver the turn off delay of power switch QD and its driver. ...

Page 101

... Output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Preliminary DS41288C-page 99 ...

Page 102

... PIC16F610/616/16HV610/616 10.4.4 ENHANCED PWM AUTO- SHUTDOWN MODE The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application ...

Page 103

... FIGURE 10-15: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1) Shutdown Event ECCPASE bit PWM Activity Start of PWM Period © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 condition PWM Period Normal PWM Shutdown Shutdown Event Occurs Event Clears PWM Period Normal PWM Shutdown ...

Page 104

... PIC16F610/616/16HV610/616 10.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE In half-bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off ...

Page 105

... Legend: – = Unimplemented locations, read as ‘0’ unchanged unknown. Shaded cells are not used by the Capture, Compare and PWM. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 R/W-0 R/W-0 PDC4 PDC3 U = Unimplemented bit, read as ‘0’ ‘0’ = Bit is cleared ...

Page 106

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 104 Preliminary © 2007 Microchip Technology Inc. ...

Page 107

... The supply voltage V constant. Therefore, the current range of the regulator is limited. Selecting a value for R three factors into consideration. Since the regulator uses the band gap voltage as the regulated voltage reference, this voltage reference is permanently enabled in the PIC16F610/16HV610 devices. Preliminary , located SER , and the V ...

Page 108

... Sleep • Code protection • ID Locations • In-Circuit Serial Programming The PIC16F610/616/16HV610/616 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a ...

Page 109

... Enabling Brown-out Reset does not automatically enable Power-up Timer. 2: The entire program memory will be erased when the code protection is turned off. 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 — — (3) PWRTE WDTE FOSC2 P = Programmable’ ...

Page 110

... Memory Programming Specification” (DS41284) and thus, does not require reprogramming. 12.3 Reset The PIC16F610/616/16HV610/616 between various kinds of Reset: a) Power-on Reset (POR) b) WDT Reset during normal operation c) WDT Reset during Sleep ...

Page 111

... For additional information, refer to Application Note AN607, “Power-up Trouble Shooting” (DS00607). 12.3.2 MCLR PIC16F610/616/16HV610/616 has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses. It should be noted that a WDT Reset does not drive MCLR pin low. ...

Page 112

... PIC16F610/616/16HV610/616 12.3.4 BROWN-OUT RESET (BOR) The BOREN0 and BOREN1 bits in the Configuration Word register select one of three BOR modes. Selecting BOREN<1:0> = 10, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. See Register 12-1 for the Configuration Word definition. A brown-out occurs when V ...

Page 113

... Then, bringing MCLR high will begin execution immediately (see Figure 12-5). This is useful for testing purposes or to synchronize more than one PIC16F610/616/ 16HV610/616 device operating in parallel. Table 12-5 shows the Reset conditions for some special registers, while Table 12-4 shows the Reset conditions for all the registers ...

Page 114

... PIC16F610/616/16HV610/616 FIGURE 12-4: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE MCLR Internal POR PWRT Time-out OST Time-out Internal Reset FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE MCLR Internal POR PWRT Time-out OST Time-out Internal Reset FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH V ...

Page 115

... See Table 12-5 for Reset value for specific condition Reset was due to brown-out, then bit All other Resets will cause bit PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 MCLR Reset WDT Reset (1) Brown-out Reset uuuu uuuu xxxx xxxx uuuu uuuu ...

Page 116

... PIC16F610/616/16HV610/616 TABLE 12-4: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED) Power-on Register Address Reset ANSEL 91h 1111 1111 (6) PR2 92h 1111 1111 WPUA 95h --11 -111 IOCA 96h --00 0000 SRCON0 99h 0000 00-0 SRCON1 9Ah 00-- ---- (6) ADRESL 9Eh xxxx xxxx (6) ADCON1 9Fh -000 ---- Legend unchanged unknown, – ...

Page 117

... Comparator Interrupts • Timer1 Overflow Interrupt • Timer2 Match Interrupt • Enhanced CCP Interrupt © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 For external interrupt events, such as the INT pin or PORTA change interrupt, the interrupt latency will be has multiple three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 12-8) ...

Page 118

... PIC16F610/616/16HV610/616 12.4.2 TIMER0 INTERRUPT An overflow (FFh → 00h) in the TMR0 register will set the T0IF bit of the INTCON register. The interrupt can be enabled/disabled by setting/clearing T0IE bit of the INTCON register. See Section 5.0 “Timer0 Module” for operation of the Timer0 module. FIGURE 12-7: ...

Page 119

... CCP1IF (1) (1) PIE1 — ADIE CCP1IE Legend unknown unchanged, – = unimplemented read as ‘0’ value depends upon condition. Shaded cells are not used by the interrupt module. Note 1: PIC16F616/16HV616 only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 (1) (2) Interrupt Latency Inst ( — Dummy Cycle ...

Page 120

... Execute the ISR code • Restore the Status (and Bank Select Bit register) • Restore the W register Note: The PIC16F610/616/16HV610/616 does not require saving the PCLATH. However, if computed GOTO’s are used in both the ISR and the main code, the PCLATH must be saved and restored in the ISR ...

Page 121

... WDT STATUS Conditions WDTE = 0 CLRWDT Command Exit Sleep + System Clock = EXTRC, INTRC, EC Exit Sleep + System Clock = XT, HS, LP © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 12.6.1 WDT PERIOD The WDT has a nominal time-out period (with no prescaler). The time-out periods vary with temperature part (see Table 15-4, Parameter 31). If longer time-out ...

Page 122

... PIC16F610/616/16HV610/616 TABLE 12-8: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER Name Bit 7 Bit 6 Bit 5 OPTION_REG RAPU INTEDG T0CS (1) CONFIG IOSCFS CP MCLRE Legend: Shaded cells are not used by the Watchdog Timer. Note 1: See Register 12-1 for operation of all Configuration Word register bits. DS41288C-page 120 ...

Page 123

... External Interrupt from INT pin. Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 When the SLEEP instruction is being executed, the next instruction ( prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled) ...

Page 124

... PIC16F610/616/16HV610/616 FIGURE 12-9: WAKE-UP FROM SLEEP THROUGH INTERRUPT OSC1 (4) CLKOUT INT pin INTF flag (INTCON reg.) GIE bit (INTCON reg.) Instruction Flow Instruction Inst(PC) = Sleep Inst( Fetched Instruction Sleep Inst(PC – 1) Executed Note 1: XT Oscillator mode assumed 1024 T (drawing not to scale). This delay does not apply to EC, INTOSC and RC Oscillator modes. ...

Page 125

... PIC16F610/616/16HV610/616 12.11 In-Circuit Debugger Since in-circuit debugging requires access to three pins, MPLAB device is not practical. A special 28-pin PIC16F610/ 616/16HV610/616 ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user. ...

Page 126

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 124 Preliminary © 2007 Microchip Technology Inc. ...

Page 127

... INSTRUCTION SET SUMMARY The PIC16F610/616/16HV610/616 instruction set is highly orthogonal and is comprised of three basic categories: • Byte-oriented operations • Bit-oriented operations • Literal and control operations Each PIC16 instruction is a 14-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction ...

Page 128

... PIC16F610/616/16HV610/616 TABLE 13-2: PIC16F610/616/16HV610/616 INSTRUCTION SET Mnemonic, Description Operands BYTE-ORIENTED FILE REGISTER OPERATIONS ADDWF f, d Add W and f ANDWF f, d AND W with f CLRF f Clear f CLRW – Clear W COMF f, d Complement f DECF f, d Decrement f DECFSZ f, d Decrement f, Skip if 0 INCF f, d Increment f INCFSZ ...

Page 129

... Z Description: AND the W register with register ‘f’. If ‘d’ is ‘0’, the result is stored in the W register. If ‘d’ is ‘1’, the result is stored back in register ‘f’. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 BCF Syntax: k Operands: Operation: Status Affected: Description: ...

Page 130

... PIC16F610/616/16HV610/616 BTFSS Bit Test f, Skip if Set Syntax: [ label ] BTFSS f,b 0 ≤ f ≤ 127 Operands: 0 ≤ b < 7 Operation: skip if (f<b> Status Affected: None Description: If bit ‘b’ in register ‘f’ is ‘0’, the next instruction is executed. If bit ‘b’ is ‘1’, then the next ...

Page 131

... Description: The contents of register ‘f’ are incremented. If ‘d’ is ‘0’, the result is placed in the W register. If ‘d’ is ‘1’, the result is placed back in register ‘f’. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 INCFSZ Syntax: Operands: Operation: Status Affected: Description: ...

Page 132

... PIC16F610/616/16HV610/616 MOVF Move f Syntax: [ label ] MOVF f,d 0 ≤ f ≤ 127 Operands: d ∈ [0,1] (f) → (dest) Operation: Status Affected: Z Description: The contents of register ‘f’ is moved to a destination dependent upon the status of ‘d’ destination is W register the destination is file register ‘f’ ...

Page 133

... Global Interrupt Enable bit, GIE (INTCON<7>). This is a two-cycle instruction. Words: 1 Cycles: 2 Example: RETFIE After Interrupt PC = TOS GIE = 1 © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 RETLW Syntax: Operands: Operation: Status Affected: Description: Words: Cycles: Example: TABLE DONE RETURN Syntax: Operands: Operation: ...

Page 134

... PIC16F610/616/16HV610/616 RLF Rotate Left f through Carry Syntax: [ label ] RLF f,d 0 ≤ f ≤ 127 Operands: d ∈ [0,1] Operation: See description below Status Affected: C Description: The contents of register ‘f’ are rotated one bit to the left through the Carry flag. If ‘d’ is ‘0’, the result is placed in the W register. If ‘ ...

Page 135

... Operation: Status Affected: Z Description: The contents of the W register are XOR’ed with the eight-bit literal ‘k’. The result is placed in the W register. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 XORWF Syntax: Operands: Operation: Status Affected: Description: Preliminary Exclusive OR W with f [ label ] XORWF f,d 0 ≤ ...

Page 136

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 134 Preliminary © 2007 Microchip Technology Inc. ...

Page 137

... MPLAB PM3 Device Programmer - PICkit™ 2 Development Programmer • Low-Cost Demonstration and Development Boards and Evaluation Kits © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 14.1 MPLAB Integrated Development Environment Software The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit micro- controller market ...

Page 138

... PIC16F610/616/16HV610/616 14.2 MPASM Assembler The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs. The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging ...

Page 139

... Microchip Technology Inc. PIC16F610/616/16HV610/616 14.9 MPLAB ICD 2 In-Circuit Debugger Microchip’s In-Circuit Debugger, MPLAB ICD powerful, low-cost, connecting to the host PC via an RS-232 or high-speed USB interface ...

Page 140

... PIC16F610/616/16HV610/616 14.11 PICSTART Plus Development Programmer The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages pins. ...

Page 141

... This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 ........................................................................... -0. )...............................................................................................................± ).........................................................................................................± ...

Page 142

... PIC16F610/616/16HV610/616 FIGURE 15-1: PIC16F610/616 VOLTAGE-FREQUENCY GRAPH, ≤ ≤ -40°C T +125°C A 5.5 5.0 4.5 4.0 3.5 3.0 2.5 2.0 0 Note 1: The shaded region indicates the permissible combinations of voltage and frequency. FIGURE 15-2: PIC16HV610/616 VOLTAGE-FREQUENCY GRAPH, ≤ ≤ -40°C T +125°C A 5.0 4 ...

Page 143

... FIGURE 15-3: PIC16F610/616 VOLTAGE-FREQUENCY GRAPH, ≤ ≤ -40°C T +125°C A 125 2.0 2.5 FIGURE 15-4: PIC16HV610/616 VOLTAGE-FREQUENCY GRAPH, ≤ ≤ -40°C T +125°C A 125 2.0 2.5 © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 ± 5% ± 2% ± 1% 3.0 3.5 4.0 4.5 V (V) DD ± 5% ± ...

Page 144

... PIC16F610/616/16HV610/616 15.1 DC Characteristics: PIC16F610/616/16HV610/616-I (Industrial) PIC16F610/616/16HV610/616-E (Extended) DC CHARACTERISTICS Param Sym Characteristic No. V Supply Voltage DD D001 PIC16F610/616 D001 PIC16HV610/616 D001B PIC16F610/616 D001B PIC16HV610/616 D001C PIC16F610/616 D001C PIC16HV610/616 D001D PIC16F610/616 D001D PIC16HV610/616 D002* V RAM Data Retention DR (1) Voltage D003 V V Start Voltage to POR ...

Page 145

... DC Characteristics: PIC16F610/616/16HV610/616-I (Industrial) PIC16F610/616/16HV610/616-E (Extended) Standard Operating Conditions (unless otherwise stated) DC CHARACTERISTICS Operating temperature Param Device Characteristics No. (1, 2) D010 Supply Current ( D011* D012 D013* D014 D016* D017 D018 D019 * These parameters are characterized but not tested. † Data in “Typ” column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested ...

Page 146

... Standard Operating Conditions (unless otherwise stated) DC CHARACTERISTICS Operating temperature Param Device Characteristics No. D020 Power-down Base (2) Current PIC16F610/616 PIC16HV610/616 D021 D022 D023 D024 D025* D026 D027 Legend: TBD = To Be Determined * These parameters are characterized but not tested. † Data in “Typ” column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested ...

Page 147

... The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied Shunt regulator is always enabled and always draws operating current. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 -E (Extended) -40°C ≤ T ≤ +125°C for extended A Min Typ† ...

Page 148

... The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages. 4: Including OSC2 in CLKOUT mode. DS41288C-page 146 PIC16F610/616/16HV610/616-I (Industrial) PIC16F610/616/16HV610/616-E (Extended) Standard Operating Conditions (unless otherwise stated) -40°C ≤ T Operating temperature -40°C ≤ T Min Typ† ...

Page 149

... Higher leakage current may be measured at different input voltages. 4: Including OSC2 in CLKOUT mode. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 PIC16F610/616/16HV610/616-I (Industrial) PIC16F610/616/16HV610/616-E (Extended) (Continued) Standard Operating Conditions (unless otherwise stated) -40°C ≤ T Operating temperature -40°C ≤ T Min Typ† ...

Page 150

... PIC16F610/616/16HV610/616 15.6 Thermal Considerations Standard Operating Conditions (unless otherwise stated) -40°C ≤ T ≤ +125°C Operating temperature A Param Sym Characteristic No. θ TH01 Thermal Resistance JA Junction to Ambient θ TH02 Thermal Resistance JC Junction to Case TH03 T Die Temperature DIE TH04 PD Power Dissipation TH05 P Internal Power Dissipation ...

Page 151

... I/O Port mc MCLR Uppercase letters and their meanings Fall H High I Invalid (High-impedance) L Low FIGURE 15-5: LOAD CONDITIONS Load Condition Pin Legend for all pins for OSC2 output © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 T Time osc OSC1 SCK T0CKI t1 T1CKI Period R Rise V Valid ...

Page 152

... PIC16F610/616/16HV610/616 15.8 AC Characteristics: PIC16F610/616/16HV610/616 (Industrial, Extended) FIGURE 15-6: CLOCK TIMING Q4 OSC1/CLKIN OSC2/CLKOUT (LP,XT,HS Modes) OSC2/CLKOUT (CLKOUT Mode) TABLE 15-1: CLOCK OSCILLATOR TIMING REQUIREMENTS Standard Operating Conditions (unless otherwise stated) -40°C ≤ T ≤ +125°C Operating temperature A Param Sym Characteristic No. OS01 F External CLKIN Frequency ...

Page 153

... When an external clock input is used, the “max” cycle time limit is “DC” (no clock) for all devices ensure these oscillator frequency tolerances, V possible. 0.1 μF and 0.01 μF values in parallel are recommended design. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Freq. Min Typ† Max Tolerance — ...

Page 154

... PIC16F610/616/16HV610/616 FIGURE 15-7: CLKOUT AND I/O TIMING Cycle Write Q4 F OSC CLKOUT I/O pin (Input) I/O pin Old Value (Output) TABLE 15-3: CLKOUT AND I/O TIMING PARAMETERS Standard Operating Conditions (unless otherwise stated) Operating Temperature -40°C ≤ T ≤ +125°C A Param ...

Page 155

... Asserted low. FIGURE 15-9: BROWN-OUT RESET TIMING AND CHARACTERISTICS BOR (Device in Brown-out Reset) Reset (due to BOR delay only if PWRTE bit in the Configuration Word register is programmed to ‘0’. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 BOR 37 33* Preliminary 31 34 HYST (Device not in Brown-out Reset) ...

Page 156

... PIC16F610/616/16HV610/616 TABLE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS Standard Operating Conditions (unless otherwise stated) -40°C ≤ T Operating Temperature A Param Sym Characteristic No MCLR Pulse Width (low Watchdog Timer Time-out WDT Period (No Prescaler Oscillation Start-up Timer ...

Page 157

... Delay from External Clock Edge to Timer TMR Increment * These parameters are characterized but not tested. † Data in “Typ” column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Min Typ† ...

Page 158

... PIC16F610/616/16HV610/616 FIGURE 15-11: CAPTURE/COMPARE/PWM TIMINGS (ECCP) CCP1 (Capture mode) Note: Refer to Figure 15-5 for load conditions. TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP) Standard Operating Conditions (unless otherwise stated) -40°C ≤ T Operating Temperature A Param Sym Characteristic No. CC01* TccL CCP1 Input Low Time CC02* ...

Page 159

... VP6 voltage output OUT VR02 V1P2 V1P2 voltage output OUT VR03 T Settling Time STABLE * These parameters are characterized but not tested. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 ≤ +125°C Min Typ† ± 5.0 — 0 — +55 — Falling — 150 Rising — ...

Page 160

... PIC16F610/616/16HV610/616 TABLE 15-10: SHUNT REGULATOR SPECIFICATIONS (PIC16HV610/616 only) SHUNT REGULATOR CHARACTERISTICS Param Symbol Characteristics No. SR01 V Shunt Voltage SHUNT SR02 I Shunt Current SHUNT SR03* T Settling Time SETTLE SR04 C Load Capacitance LOAD ΔI SR05 Regulator operating current SNT * These parameters are characterized but not tested. ...

Page 161

... Note 1: ADRESH and ADRESL registers may be read on the following T 2: See Section 9.3 “A/D Acquisition Requirements” for minimum conditions. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 ≤ +125°C Min Typ† Max Units μs 1.6 — ...

Page 162

... PIC16F610/616/16HV610/616 FIGURE 15-12: PIC16F616/16HV616 A/D CONVERSION TIMING (NORMAL MODE) BSF ADCON0, GO AD134 (T OSC Q4 A/D CLK A/D Data ADRES ADIF GO AD132 Sample Note 1: If the A/D clock source is selected as RC, a time of T SLEEP instruction to be executed. FIGURE 15-13: PIC16F616/16HV616 A/D CONVERSION TIMING (SLEEP MODE) ...

Page 163

... DC AND AC CHARACTERISTICS GRAPHS AND TABLES Graphs are not available at this time. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Preliminary DS41288C-page 161 ...

Page 164

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 162 Preliminary © 2007 Microchip Technology Inc. ...

Page 165

... For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 Example PIC16F616 -I/P 0610017 Example ...

Page 166

... PIC16F610/616/16HV610/616 17.2 Package Details The following sections give the technical details of the packages. 8-Lead Plastic Dual In-Line (P or PA) – 300 mil Body [PDIP] Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging N NOTE Number of Pins ...

Page 167

... Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side. 4. Dimensioning and tolerancing per ASME Y14.5M. BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 φ ...

Page 168

... PIC16F610/616/16HV610/616 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP] Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging D N NOTE Number of Pins Pitch Overall Height Molded Package Thickness Standoff Overall Width Molded Package Width ...

Page 169

... Pin 1 visual index feature may vary, but must be located within the hatched area. 2. Package is saw singulated. 3. Dimensioning and tolerancing per ASME Y14.5M. BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 EXPOSED PAD ...

Page 170

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 168 Preliminary © 2007 Microchip Technology Inc. ...

Page 171

... APPENDIX A: DATA SHEET REVISION HISTORY Revision A This is a new data sheet. Revision B (12/06) Added PIC16F610/16HV610 parts. Replaced Package Drawings. Revision C (03/2007) Replaced Package Drawings (Rev. AM); Replaced Development Support Section; Revised Product ID System. B.1 PIC16F676 to PIC16F610/616/16HV610/616 TABLE B-1: FEATURE COMPARISON Feature Max Operating Speed ...

Page 172

... PIC16F610/616/16HV610/616 NOTES: DS41288C-page 170 Preliminary © 2007 Microchip Technology Inc. ...

Page 173

... Comparator C2 ........................................................... 56 Compare ..................................................................... 86 Crystal Operation ........................................................ 27 External RC Mode....................................................... 28 In-Circuit Serial Programming Connections.............. 123 Interrupt Logic ........................................................... 116 MCLR Circuit............................................................. 109 On-Chip Reset Circuit ............................................... 108 PIC16F610/16HV610.................................................... 7 PIC16F616/16HV616.................................................... 8 PWM (Enhanced)........................................................ 91 RA0 and RA1 Pins ...................................................... 34 RA2 Pins ..................................................................... 35 RA3 Pin....................................................................... 36 RA4 Pin....................................................................... 37 RA5 Pin....................................................................... 38 RC0 and RC1 Pins...................................................... 41 © ...

Page 174

... PIC16F610/616/16HV610/616 Initializing PORTA ....................................................... 31 Initializing PORTC....................................................... 40 Saving Status and W Registers in RAM ................... 118 Code Protection ................................................................ 122 Comparator C2OUT as T1 Gate ..................................................... 63 Operation .................................................................... 55 Operation During Sleep .............................................. 59 Response Time ........................................................... 57 Synchronizing COUT w/Timer1 .................................. 63 Comparator Analog Input Connection Considerations........ 62 Comparator Hysteresis ....................................................... 64 Comparator Module ............................................................ 55 Associated registers.................................................... 65 C1 Output State Versus Input Conditions ................... 57 ...

Page 175

... ANSEL (Analog Select) .............................................. 32 CCP1CON (Enhanced CCP1 Control) ....................... 83 CM1CON0 (C1 Control) ............................................. 60 CM2CON0 (C2 Control) ............................................. 61 CM2CON1 (C2 Control) ............................................. 63 CONFIG (Configuration Word) ................................. 107 Data Memory Map (PIC16F610/16HV610) ................ 13 Data Memory Map (PIC16F616/16HV616) ................ 13 ECCPAS (Enhanced CCP Auto-shutdown Control) . 100 INTCON (Interrupt Control) ........................................ 18 IOCA (Interrupt-on-Change PORTA).......................... 33 OPTION_REG (OPTION)..................................... 17, 45 OSCTUNE (Oscillator Tuning).................................... 29 PCON (Power Control Register) ...

Page 176

... PIC16F610/616/16HV610/616 Special Function Registers ......................................... 12 Special Register Summary ......................................... 15 SRCON0 (SR Latch Control 0) ................................... 67 SRCON1 (SR Latch Control 1) ................................... 67 STATUS ...................................................................... 16 T1CON ........................................................................ 50 T2CON ........................................................................ 54 TRISA (Tri-State PORTA) ........................................... 31 TRISC (Tri-State PORTC) .......................................... 40 VRCON (Voltage Reference Control) ......................... 70 WPUA (Weak Pull Up PORTA)................................... 33 Reset................................................................................. 108 Revision History ................................................................ 169 S Shoot-through Current ...................................................... 102 Sleep Power-Down Mode ...

Page 177

... To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions. © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 CUSTOMER SUPPORT Users of Microchip products can receive assistance through several channels: • Distributor or Representative • ...

Page 178

... Telephone: (_______) _________ - _________ Application (optional): Would you like a reply? Y Device: PIC16F610/616/16HV610/616 Questions: 1. What are the best features of this document? 2. How does this document meet your hardware and software development needs you find the organization of this document easy to follow? If not, why? 4 ...

Page 179

... QTP, SQTP or ROM Code; Special Requirements (blank otherwise) © 2007 Microchip Technology Inc. PIC16F610/616/16HV610/616 XXX Examples: Pattern a) PIC16F610/616/16HV610/616-E/P Extended Temp., PDIP package, 20 MHz, QTP pattern #301 b) PIC16F610/616/16HV610/616-I/SL = Industrial Temp., SOIC package, 20 MHz (Industrial) (Extended) Note 1: T packages only. Preliminary . 301 = = in tape and reel TSSOP and SOIC ...

Page 180

... Taiwan - Kaohsiung Tel: 886-7-536-4818 Fax: 886-7-536-4803 Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102 Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350 Preliminary © 2007 Microchip Technology Inc. EUROPE Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 ...