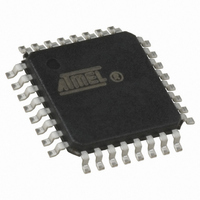

AT89LP428-20AU Atmel, AT89LP428-20AU Datasheet - Page 74

AT89LP428-20AU

Manufacturer Part Number

AT89LP428-20AU

Description

MCU 8051 4K FLASH SPI 32TQFP

Manufacturer

Atmel

Series

89LPr

Datasheet

1.AT89LP428-20AU.pdf

(149 pages)

Specifications of AT89LP428-20AU

Core Processor

8051

Core Size

8-Bit

Speed

20MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

30

Program Memory Size

4KB (4K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFP, 32-VQFP

Processor Series

AT89x

Core

8051

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

AT89ISP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89LP428-20AU

Manufacturer:

RFMD

Quantity:

1 240

Figure 13-14. Three-Phase Mode with Channel B Disabled

14. External Interrupts

15. General-purpose Interrupts

74

AT89LP428/828

PHSD

CCA

CCB

CCC

The INT0 (P3.2) and INT1 (P3.3) pins of the AT89LP428/828 may be used as external interrupt

sources. The external interrupts can be programmed to be level-activated or transition-activated

by setting or clearing bit IT1 or IT0 in Register TCON. If ITx = 0, external interrupt x is triggered

by a detected low at the INTx pin. If ITx = 1, external interrupt x is edge-triggered. In this mode if

successive samples of the INTx pin show a high in one cycle and a low in the next cycle, inter-

rupt request flag IEx in TCON is set. Flag bit IEx then requests the interrupt. Since the external

interrupt pins are sampled once each clock cycle, an input high or low should hold for at least 2

oscillator periods to ensure sampling. If the external interrupt is transition-activated, the external

source has to hold the request pin high for at least two clock cycles, and then hold it low for at

least two clock cycles to ensure that the transition is seen so that interrupt request flag IEx will

be set. IEx will be automatically cleared by the CPU when the service routine is called if gener-

ated in edge-triggered mode. If the external interrupt is level-activated, the external source has

to hold the request active until the requested interrupt is actually generated. Then the external

source must deactivate the request before the interrupt service routine is completed, or else

another interrupt will be generated. Both INT0 and INT1 may wake up the device from the

Power-down state.

The GPI function provides 8 configurable external interrupts on Port 1. Each port pin can detect

high/low levels or positive/negative edges. The GPIEN register select which bits of Port 1 are

enabled to generate an interrupt. The GPMOD and GPLS registers determine the mode for each

individual pin. GPMOD selects between level-sensitive and edge-triggered mode. GPLS selects

between high/low in level mode and positive/negative in edge mode. A block diagram is shown

in

level must appear in two successive samples before generating the interrupt. In edge-triggered

mode, a transition will be detected if the value changes from one sample to the next. When an

interrupt condition on a pin is detected, and that pin is enabled, the appropriate flag in the GPIF

register is set. The flags in GPIF must be cleared by software. Any GPI interrupt may wake up

the device from the Power-down state.

Figure

15-1. The pins of Port 1 are sampled every clock cycle. In level-sensitive mode, a valid

PHS = 010B, CCB Disabled

3654A–MICRO–8/09