PIC16C505-04I/P Microchip Technology, PIC16C505-04I/P Datasheet - Page 34

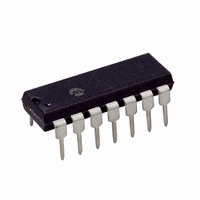

PIC16C505-04I/P

Manufacturer Part Number

PIC16C505-04I/P

Description

IC MCU OTP 1KX12 14DIP

Manufacturer

Microchip Technology

Series

PIC® 16Cr

Specifications of PIC16C505-04I/P

Program Memory Type

OTP

Program Memory Size

1.5KB (1K x 12)

Package / Case

14-DIP (0.300", 7.62mm)

Core Processor

PIC

Core Size

8-Bit

Speed

4MHz

Peripherals

POR, WDT

Number Of I /o

11

Ram Size

72 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

PIC16C

Core

PIC

Data Bus Width

8 bit

Data Ram Size

72 B

Maximum Clock Frequency

4 MHz

Number Of Programmable I/os

12

Number Of Timers

1

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

3rd Party Development Tools

52715-96, 52716-328, 52717-734

Development Tools By Supplier

ICE2000

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

ISPICR1 - ADAPTER IN-CIRCUIT PROGRAMMING309-1086 - ADAPTER 14-ZIF BD W/14-SO PLUGS309-1085 - ADAPTER 14-DIP BD W/2 14-SO PLUGAC124001 - MODULE SKT PROMATEII 8DIP/SOIC

Eeprom Size

-

Data Converters

-

Connectivity

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PIC16C505-04I/P

Manufacturer:

BOURNS

Quantity:

1 001

Part Number:

PIC16C505-04I/P

Manufacturer:

MICROCHIP/微芯

Quantity:

20 000

PIC16C505

FIGURE 7-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO V

7.5

In the PIC16C505, the DRT runs any time the device is

powered up. DRT runs from RESET and varies based

on oscillator selection and reset type (see Table 7-5).

The DRT operates on an internal RC oscillator. The

processor is kept in RESET as long as the DRT is

active. The DRT delay allows V

min. and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic

resonators require a certain time after power-up to

establish a stable oscillation. The on-chip DRT keeps

the device in a RESET condition for approximately 18

ms after MCLR has reached a logic high (V

level. Thus, programming RB3/MCLR/V

and using an external RC network connected to the

MCLR input is not required in most cases, allowing for

savings in cost-sensitive and/or space restricted

applications, as well as allowing the use of the RB3/

MCLR/V

The Device Reset time delay will vary from chip to chip

due to V

AC parameters for details.

The DRT will also be triggered upon a Watchdog

Timer time-out. This is particularly important for

applications using the WDT to wake from SLEEP

mode automatically.

Reset sources are POR, MCLR, WDT time-out and

Wake-up on pin change. (See Section 7.9.2, Notes 1,

2, and 3, page 37.)

DS40192C-page 34

INTERNAL RESET

INTERNAL POR

DRT TIME-OUT

PP

Device Reset Timer (DRT)

DD

Note:

pin as a general purpose input.

, temperature and process variation. See

MCLR

V

DD

When V

value. In this example, the chip will reset properly if, and only if, V1

DD

rises slowly, the T

DD

to rise above V

PP

as MCLR

T

IH

DRT

MCLR)

V1

DRT

DD

time-out expires long before V

7.6

The Watchdog Timer (WDT) is a free running on-chip

RC oscillator, which does not require any external

components. This RC oscillator is separate from the

external RC oscillator of the RB5/OSC1/CLKIN pin

and the internal 4 MHz oscillator. That means that the

WDT will run even if the main processor clock has

been stopped, for example, by execution of a SLEEP

instruction. During normal operation or SLEEP, a WDT

reset or wake-up reset generates a device RESET.

The TO bit (STATUS<4>) will be cleared upon a

Watchdog Timer reset.

The

programming the configuration bit WDTE as a ’0’

(Section 7.1). Refer to the PIC16C505 Programming

Specifications to determine how to access the

configuration word.

TABLE 7-5:

Configuration

IntRC &

ExtRC

HS, XT & LP

Oscillator

WDT

Watchdog Timer (WDT)

can

DRT (DEVICE RESET TIMER

PERIOD)

18 ms (typical)

18 ms (typical)

be

POR Reset

DD

DD

): SLOW V

V

permanently

1999 Microchip Technology Inc.

has reached its final

DD

min.

DD

18 ms (typical)

Subsequent

RISE TIME

(typical)

disabled

Resets

300 µs

by