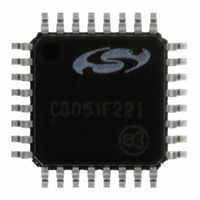

C8051F221-GQR Silicon Laboratories Inc, C8051F221-GQR Datasheet - Page 111

C8051F221-GQR

Manufacturer Part Number

C8051F221-GQR

Description

IC 8051 MCU 8K FLASH 32LQFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F2xxr

Specifications of C8051F221-GQR

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, WDT

Number Of I /o

22

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 22x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

C8051F2x

Core

8051

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

SPI, UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

32

Number Of Timers

3 bit

Operating Supply Voltage

2.7 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F226DK

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 32 Channel

For Use With

336-1241 - DEV KIT F220/221/226/230/231/236

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F221-GQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

15.1. Signal Descriptions

The four signals used by the SPI (MOSI, MISO, SCK, NSS) are described below.

15.1.1. Master Out, Slave In

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It

is used to serially transfer data from the master to the slave. Data is transferred most-significant bit first.

15.1.2. Master In, Slave Out

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device.

It is used to serially transfer data from the slave to the master. Data is transferred most-significant bit first.

A SPI slave places the MISO pin in a high-impedance state when the slave is not selected.

15.1.3. Serial Clock

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used

to synchronize the transfer of data between the master and slave on the MOSI and MISO lines.

15.1.4. Slave Select

The slave select (NSS) signal is an input used to select the SPI module when in slave mode by a master,

or to disable the SPI module when in master mode. When in slave mode, it is pulled low to initiate a data

transfer and remains low for the duration of the transfer.

Master

Device

Device

Slave

Figure 15.2. SPI Block Diagram

NSS

Device

Slave

Rev. 1.6

NSS

Device

Slave

NSS

VDD

C8051F2xx

MISO

MOSI

SCK

111