MCF51JE256VML Freescale Semiconductor, MCF51JE256VML Datasheet - Page 34

MCF51JE256VML

Manufacturer Part Number

MCF51JE256VML

Description

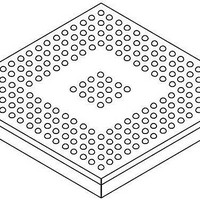

IC MCU 256K COLDF 104-PBGA

Manufacturer

Freescale Semiconductor

Series

MCF51JEr

Datasheet

1.TWR-MCF51JE.pdf

(50 pages)

Specifications of MCF51JE256VML

Core Processor

Coldfire V1

Core Size

32-Bit

Speed

50MHz

Connectivity

CAN, EBI/EMI, I²C, SCI, SPI, USB OTG

Peripherals

LVD, PWM, WDT

Number Of I /o

69

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 12x12b, D/A 1x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 105°C

Package / Case

104-LFBGA

Core

ColdFire V1

Data Bus Width

32 bit

Data Ram Size

32 KB

Interface Type

SPI, SCI, I2C

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

69

Number Of Timers

2

Operating Supply Voltage

1.8 V to 3.6 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCF51JE256VML

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Preliminary Electrical Characteristics

2

3

4

5

6

7

1-3

This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is

changed, DRS bit is changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a

crystal/resonator is being used as the reference, this specification assumes it is already running.

This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE,

BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already

running.

Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f

Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected

into the FLL circuitry via V

625 ns represents 5 time quanta for CAN applications, under worst-case conditions of 8 MHz CAN bus clock, 1 Mbps CAN Bus

speed, and 8 time quanta per bit for bit time settings. 5 time quanta is the minimum time between a synchronization edge and the

sample point of a bit using 8 time quanta per bit.

Below D

already in lock, then the MCG may stay in lock.

Below D

#

1

2

3

4

5

Oscillator crystal or resonator

(EREFS = 1, ERCLKEN = 1)

Load capacitors

Feedback resistor

Series resistor — Low range

Series resistor — High range

lock

unl

minimum, the MCG will not exit lock if already in lock. Above D

minimum, the MCG is guaranteed to enter lock. Above D

DD

Table 18. XOSC (Temperature Range = –40 to 105

and V

SS

Characteristic

and variation in crystal oscillator frequency increase the C

Low range

(32 kHz to 38.4 kHz)

High range

(1 MHz to 16 MHz)

Low Gain (HGO = 0)

High Gain (HGO = 1)

• Low range (RANGE = 0)

• High range (RANGE = 1),

• FEE or FBE mode

• High range (RANGE = 1),

• High gain (HGO = 1),

• FBELP mode

• High range (RANGE = 1),

• Low power (HGO = 0),

• FBELP mode

• Low Gain (HGO = 0)

• High Gain (HGO = 1)

Preliminary — Subject to Change

≥ 8 MHz

4 MHz

1 MHz

2

lock

maximum, the MCG will not enter lock. But if the MCG is

unl

maximum, the MCG is guaranteed to exit lock.

Symbol

R

R

C

C

R

fhi

fhi

fhi

—

f

lo

S

S

1

2

F

°

C Ambient)

Jitter

Min

32

—

—

—

—

—

—

—

1

1

1

percentage for a given interval.

Typ

100

10

—

—

—

—

See Note

1

0

0

0

0

Freescale Semiconductor

1

BUS

.

3

Max

38.4

16

10

20

—

—

—

—

5

8

0

MHz

MHz

MHz

Unit

kHz

MΩ

kΩ

kΩ