AGLN020V5-QNG68 Actel, AGLN020V5-QNG68 Datasheet - Page 65

AGLN020V5-QNG68

Manufacturer Part Number

AGLN020V5-QNG68

Description

FPGA - Field Programmable Gate Array 20K System Gates IGLOO nano

Manufacturer

Actel

Datasheet

1.AGLN030V5-ZUCG81.pdf

(140 pages)

Specifications of AGLN020V5-QNG68

Processor Series

AGLN020

Core

IP Core

Number Of Macrocells

172

Maximum Operating Frequency

250 MHz

Number Of Programmable I/os

49

Supply Voltage (max)

1.5 V

Supply Current

6 uA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

- 20 C

Development Tools By Supplier

AGLN-Nano-Kit, AGLN-Z-Nano-Kit, AGL-Dev-Kit-SCS, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FLASHPRO 4, FlashPro 3, FLASHPRO LITE

Mounting Style

SMD/SMT

Supply Voltage (min)

1.425 V

Number Of Gates

20 K

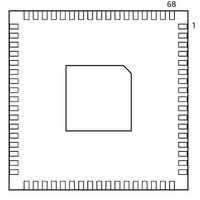

Package / Case

QFN-68

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AGLN020V5-QNG68

Manufacturer:

SILICON

Quantity:

4 500

Company:

Part Number:

AGLN020V5-QNG68

Manufacturer:

EVERSPIN

Quantity:

5 600

- Current page: 65 of 140

- Download datasheet (5Mb)

Figure 2-17 • Input DDR Timing Model

Table 2-78 • Parameter Definitions

Parameter Name

t

t

t

t

t

t

t

t

DDRICLKQ1

DDRICLKQ2

DDRISUD

DDRIHD

DDRICLR2Q1

DDRICLR2Q2

DDRIREMCLR

DDRIRECCLR

CLK

Data

CLR

DDR Module Specifications

Note:

Input DDR Module

INBUF

CLKBUF

DDR is not supported for AGLN010, AGLN015, and AGLN020 devices.

INBUF

Clock-to-Out Out_QR

Clock-to-Out Out_QF

Data Setup Time of DDR input

Data Hold Time of DDR input

Clear-to-Out Out_QR

Clear-to-Out Out_QF

Clear Removal

Clear Recovery

A

B

C

Parameter Definition

Input DDR

R ev i si o n 1 1

DDR_IN

FF1

FF2

Measuring Nodes (from, to)

IGLOO nano Low Power Flash FPGAs

D

E

C, D

B, D

B, E

A, B

A, B

C, E

C, B

C, B

Out_QF

(to core)

Out_QR

(to core)

2- 51

Related parts for AGLN020V5-QNG68

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

AGLN020V5-QNG68I

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

BGA 81/IC,FPGA,520-CELL,CMOS

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 20K System Gates IGLOO nano

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Silicon Sculptor Programming Mod

Manufacturer:

Actel

Part Number:

Description:

MCU, MPU & DSP Development Tools InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators PQ160 Module

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators AFDX Solutions

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators SILICON SCULPTOR ADAPTER MODULE

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Silicon Sculptor Software

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel