CY7C1315BV18-200BZC Cypress Semiconductor Corp, CY7C1315BV18-200BZC Datasheet - Page 8

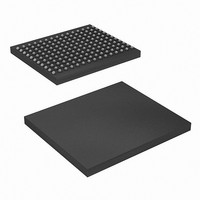

CY7C1315BV18-200BZC

Manufacturer Part Number

CY7C1315BV18-200BZC

Description

SRAM (Static RAM)

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CY7C1313BV18-167BZC.pdf

(28 pages)

Specifications of CY7C1315BV18-200BZC

Format - Memory

RAM

Memory Type

SRAM - Synchronous, QDR II

Memory Size

18M (512K x 36)

Speed

200MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.9 V

Operating Temperature

0°C ~ 70°C

Package / Case

165-LFBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C1315BV18-200BZC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document Number: 38-05620 Rev. *C

will be valid 0.45 ns from the rising edge of the output clock (C

or C or (K or K when in single-clock mode)). In order to

maintain the internal logic, each read access must be allowed

to complete. Each Read access consists of four 18-bit data

words and takes 2 clock cycles to complete. Therefore, Read

accesses to the device can not be initiated on two consecutive

K clock rises. The internal logic of the device will ignore the

second Read request. Read accesses can be initiated on

every other K clock rise. Doing so will pipeline the data flow

such that data is transferred out of the device on every rising

edge of the output clocks (C and C or K and K when in

single-clock mode).

When the read port is deselected, the CY7C1313BV18 will first

complete the pending Read transactions. Synchronous

internal circuitry will automatically tri-state the outputs following

the next rising edge of the Positive Output Clock (C). This will

allow for a seamless transition between devices without the

insertion of wait states in a depth expanded memory.

Write Operations

Write operations are initiated by asserting WPS active at the

rising edge of the Positive Input Clock (K). On the following K

clock rise the data presented to D

into the lower 18-bit Write Data register, provided BWS

both asserted active. On the subsequent rising edge of the

Negative Input Clock (K) the information presented to D

is also stored into the Write Data register, provided BWS

are both asserted active. This process continues for one more

cycle until four 18-bit words (a total of 72 bits) of data are

stored in the SRAM. The 72 bits of data are then written into

the memory array at the specified location. Therefore, Write

accesses to the device can not be initiated on two consecutive

K clock rises. The internal logic of the device will ignore the

second Write request. Write accesses can be initiated on

every other rising edge of the Positive Input Clock (K). Doing

so will pipeline the data flow such that 18 bits of data can be

transferred into the device on every rising edge of the input

clocks (K and K).

When deselected, the Write port will ignore all inputs after the

pending Write operations have been completed.

Byte Write Operations

Byte Write operations are supported by the CY7C1313BV18.

A Write operation is initiated as described in the Write Opera-

tions section above. The bytes that are written are determined

by BWS

data words. Asserting the appropriate Byte Write Select input

during the data portion of a Write will allow the data being

presented to be latched and written into the device.

Deasserting the Byte Write Select input during the data portion

of a write will allow the data stored in the device for that byte

to remain unaltered. This feature can be used to simplify

Read/Modify/Write operations to a Byte Write operation.

Single Clock Mode

The CY7C1313BV18 can be used with a single clock that

controls both the input and output registers. In this mode the

device will recognize only a single pair of input clocks (K and

K) that control both the input and output registers. This

operation is identical to the operation if the device had zero

skew between the K/K and C/C clocks. All timing parameters

remain the same in this mode. To use this mode of operation,

0

and BWS

1

, which are sampled with each set of 18-bit

[17:0]

is latched and stored

[1:0]

[17:0]

[1:0]

are

the user must tie C and C HIGH at power on. This function is

a strap option and not alterable during device operation.

Concurrent Transactions

The Read and Write ports on the CY7C1313BV18 operate

completely independently of one another. Since each port

latches the address inputs on different clock edges, the user

can Read or Write to any location, regardless of the transaction

on the other port. If the ports access the same location when a

Read follows a Write in successive clock cycles, the SRAM will

deliver the most recent information associated with the

specified address location. This includes forwarding data from

a Write cycle that was initiated on the previous K clock rise.

Read accesses and Write access must be scheduled such that

one transaction is initiated on any clock cycle. If both ports are

selected on the same K clock rise, the arbitration depends on

the previous state of the SRAM. If both ports were deselected,

the Read port will take priority. If a Read was initiated on the

previous cycle, the Write port will assume priority (since Read

operations can not be initiated on consecutive cycles). If a

Write was initiated on the previous cycle, the Read port will

assume priority (since Write operations can not be initiated on

consecutive cycles). Therefore, asserting both port selects

active from a deselected state will result in alternating

Read/Write operations being initiated, with the first access

being a Read.

Depth Expansion

The CY7C1313BV18 has a Port Select input for each port.

This allows for easy depth expansion. Both Port Selects are

sampled on the rising edge of the Positive Input Clock only (K).

Each port select input can deselect the specified port.

Deselecting a port will not affect the other port. All pending

transactions (Read and Write) will be completed prior to the

device being deselected.

Programmable Impedance

An external resistor, RQ, must be connected between the ZQ

pin on the SRAM and V

output driver impedance. The value of RQ must be 5X the

value of the intended line impedance driven by the SRAM. The

allowable range of RQ to guarantee impedance matching with

a tolerance of ±15% is between 175Ω and 350Ω

V

cycles upon power-up to account for drifts in supply voltage

and temperature.

Echo Clocks

Echo clocks are provided on the QDR-II to simplify data

capture on high-speed systems. Two echo clocks are

generated by the QDR-II. CQ is referenced with respect to C

and CQ is referenced with respect to C. These are free running

clocks and are synchronized to the output clock of the QDR-II.

In the single clock mode, CQ is generated with respect to K

and CQ is generated with respect to K. The timings for the

echo clocks are shown in the AC Timing table.

DDQ

= 1.5V. The output impedance is adjusted every 1024

SS

to allow the SRAM to adjust its

CY7C1313BV18

CY7C1315BV18

CY7C1311BV18

CY7C1911BV18

Page 8 of 28

,

with

[+] Feedback