CYD18S72V-100BBI Cypress Semiconductor Corp, CYD18S72V-100BBI Datasheet - Page 21

CYD18S72V-100BBI

Manufacturer Part Number

CYD18S72V-100BBI

Description

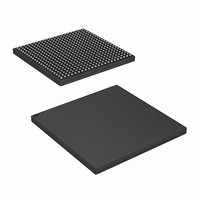

IC,SYNC SRAM,256KX72,CMOS,BGA,484PIN,PLASTIC

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CYD09S72V-133BBC.pdf

(26 pages)

Specifications of CYD18S72V-100BBI

Format - Memory

RAM

Memory Type

SRAM - Dual Port, Synchronous

Memory Size

18M (256K x 72)

Speed

100MHz

Interface

Parallel

Voltage - Supply

3.135 V ~ 3.465 V

Operating Temperature

-40°C ~ 85°C

Package / Case

484-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CYD18S72V-100BBI

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CYD18S72V-100BBI

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Switching Waveforms

Notes

Document Number : 38-06069 Rev. *K

Left_Port (L_Port) Write to Right_Port (R_Port) Read

45. CE

46. This timing is valid when one port is writing, and other port is reading the same location at the same time. If t

47. If t

CLK

L_PORT

ADDRESS

R/W

L_PORT

DATA

CLK

R_PORT

ADDRESS

R/W

R_PORT

DATA

If t

CCS

CCS

0

L

L

R

R

= OE = ADS = CNTEN = BE0 – BE7 = LOW; CE

IN

OUT

< minimum specified value, then R_Port will Read the most recent data (written by L_Port) only (2 * t

> minimum specified value, then R_Port will Read the most recent data (written by L_Port) (t

t

CKHZ

t

CH2

t

t

CH2

CYC2

t

t

CYC2

CL2

t

SW

t

t

SD

SA

t

(continued)

CL2

D

A

n

n

t

HA

t

CCS

t

SA

1

= CNTRST = MRST = CNT/MSK = HIGH.

t

HW

t

HD

A

n

t

HA

[45, 46, 47]

t

CKLZ

t

DC

t

CD2

CYC2

+ t

CYC2

CD2

CCS

Q

n

) after the rising edge of R_Port's clock.

is violated, indeterminate data will be Read out.

+ t

CD2

) after the rising edge of R_Port's clock.

CYD04S72V

CYD09S72V

CYD18S72V

Page 21 of 26

[+] Feedback