KSZ8841-16MBL Micrel Inc, KSZ8841-16MBL Datasheet - Page 35

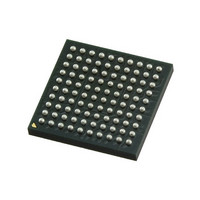

KSZ8841-16MBL

Manufacturer Part Number

KSZ8841-16MBL

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8841-16MBL.pdf

(105 pages)

Specifications of KSZ8841-16MBL

Controller Type

Ethernet Controller, MAC

Interface

Bus

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

100

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Supply

-

Lead Free Status / Rohs Status

Compliant

Other names

576-3075

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

KSZ8841-16MBL

Manufacturer:

MICREL/麦瑞

Quantity:

20 000

Regardless of whether the transfer is synchronous or asynchronous, if the address latch is required, use the rising edge of

ADSN to latch the incoming signals A[15:1], AEN, BE3N, BE2N, BE1N, and BE0N.

Note: If the local device decoder is used in either synchronous or asynchronous transfers, LDEVN will be asserted to

indicate that the KSZ8841M is successfully targeted. The signal LDEVN is a combinatorial decode of AEN and A[15:4].

Asynchronous Interface

For asynchronous transfers, the asynchronous dedicated signals RDN (for read) or WRN (for write) toggle, but the

synchronous dedicated signals CYCLEN, SWR, and RDYRTNN are de-asserted and stay at the same logic level

throughout the entire asynchronous transfer.

There is no data burst support for asynchronous transfer. All asynchronous transfers are single-data transfers. The BIU,

however, provides flexible asynchronous interfacing to communicate with various applications and architectures. Three

major ways of interfacing with the system (host) are.

1. Interfacing with the system/host relying on local device decoding and having stable address throughout the whole

Interfacing with the system/host relying on local device decoding but not having stable address throughout the entire

transfer: The typical example for this application is EISA-like bus (non-burst) interface as shown in the Figure 14. This

type of interface requires ADSN to latch the address on the rising edge. The BIU decodes latched A[15:4] and qualifies

with AEN to determine if the KSZ8841M device is the intended target. The data transfer is the same as the first case.

Interfacing with the system/host relying on central decoding (KSZ8841-32MQL only).

The typical example for this application is for an embedded processor having a central decoder on the system board or

within the processor. Connecting the chip select (CS) from system/host to DATACSN bypasses the local device decoder.

When the DATACSN is asserted, it only allows access to the Data Register in 32 bits and BE3N, BE2N, BE1N, and BE0N

are ignored as shown in the Figure 15. No other registers can be accessed by asserting DATACSN. The data transfer is

the same as in the first case. Independent of the type of asynchronous interface used. To insert a wait state, the BIU will

assert ARDY to prolong the cycle.

October 2007

Micrel, Inc.

transfer: The typical example for this application is ISA-like bus interface using latched address signals as shown

in Figure 13. No additional address latch is required, therefore ADSN should be connected Low. The BIU decodes

A[15:4] and qualifies with AEN (Address Enable) to determine if the KSZ8841M device is the intended target. The

host utilizes the rising edge of RDN to latch read data and the BIU will use rising edge of WRN to latch write data.

Signal

BCLK

Asynchronous Transfer Signals

RDN

WRN

ARDY

Note 1: I = Input. O = Output. I/O = Bi-directional.

Type

I

I

I

O

(1)

Table 2. Bus Interface Unit Signal Grouping

Function

For burst access: exactly like EXRDY signal in EISA to insert wait states. Note that

the wait states are inserted by system logic (memory) not by KSZ8841M.

Bus Clock

Asynchronous Read

Asynchronous Write

Asynchronous Ready

This signal is asserted (Low) to insert wait states.

35

KSZ8841-16/32 MQL/MVL/MBL

M9999-102207-1.6