M4A5-64/32-10VC LATTICE SEMICONDUCTOR, M4A5-64/32-10VC Datasheet - Page 7

M4A5-64/32-10VC

Manufacturer Part Number

M4A5-64/32-10VC

Description

CPLD ispMACH™ 4A Family 2.5K Gates 64 Macro Cells 83.3MHz/118MHz EECMOS Technology 5V 44-Pin TQFP Tray

Manufacturer

LATTICE SEMICONDUCTOR

Datasheet

1.M4A5-6432-10JNC.pdf

(62 pages)

Specifications of M4A5-64/32-10VC

Package

44TQFP

Family Name

ispMACHÂ 4A

Device System Gates

2500

Number Of Macro Cells

64

Maximum Propagation Delay Time

10 ns

Number Of User I/os

32

Typical Operating Supply Voltage

5 V

Maximum Operating Frequency

83.3|118 MHz

Number Of Product Terms Per Macro

20

Re-programmability Support

Yes

Operating Temperature

0 to 70 °C

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M4A5-64/32-10VC

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Part Number:

M4A5-64/32-10VC

Manufacturer:

LATTICE/莱迪斯

Quantity:

20 000

Company:

Part Number:

M4A5-64/32-10VC48

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Part Number:

M4A5-64/32-10VC48

Manufacturer:

MACNICA

Quantity:

20 000

Product-Term Array

The product-term array consists of a number of product terms that form the basis of the logic being

implemented. The inputs to the AND gates come from the central switch matrix (Table 5), and are provided

in both true and complement forms for efficient logic implementation.

Logic Allocator

Within the logic allocator, product terms are allocated to macrocells in “product term clusters.” The

availability and distribution of product term clusters are automatically considered by the software as it fits

functions within a PAL block. The size of a product term cluster has been optimized to provide high

utilization of product terms, making complex functions using many product terms possible. Yet when few

product terms are used, there will be a minimal number of unused—or wasted—product terms left over.

The product term clusters available to each macrocell within a PAL block are shown in Tables 6 and 7.

Each product term cluster is associated with a macrocell. The size of a cluster depends on the configuration

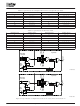

of the associated macrocell. When the macrocell is used in synchronous mode

(Figure 2a), the basic cluster has 4 product terms. When the associated macrocell is used in asynchronous

mode (Figure 2b), the cluster has 2 product terms. Note that if the product term cluster is routed to a

different macrocell, the allocator configuration is not determined by the mode of the macrocell actually

being driven. The configuration is always set by the mode of the macrocell that the cluster will drive if not

routed away, regardless of the actual routing.

In addition, there is an extra product term that can either join the basic cluster to give an extended cluster,

or drive the second input of an exclusive-OR gate in the signal path. If included with the basic cluster, this

provides for up to 20 product terms on a synchronous function that uses four extended 5-product-term

clusters. A similar asynchronous function can have up to 18 product terms.

When the extra product term is used to extend the cluster, the value of the second XOR input can be

programmed as a 0 or a 1, giving polarity control. The possible configurations of the logic allocator are

shown in Figures 3 and 4.

M4A3-32/32 and M4A5-32/32

M4A3-64/32 and M4A5-64/32

M4A3-64/64

M4A3-96/48 and M4A5-96/48

M4A3-128/64 and M4A5-128/64

M4A3-192/96 and M4A5-192/96

M4A3-256/128 and M4A5-256/128

M4A3-256/160 and M4A3-256/192

M4A3-384

M4A3-512

Device

Table 5. PAL Block Inputs

ispMACH 4A Family

Number of Inputs to PAL Block

33

33

33

33

33

34

34

36

36

36

7