XC4VLX60-11FFG668C Xilinx Inc, XC4VLX60-11FFG668C Datasheet - Page 36

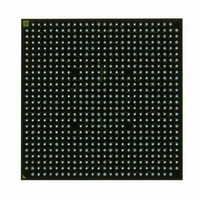

XC4VLX60-11FFG668C

Manufacturer Part Number

XC4VLX60-11FFG668C

Description

FPGA Virtex®-4 Family 59904 Cells 90nm (CMOS) Technology 1.2V 668-Pin FCBGA

Manufacturer

Xilinx Inc

Series

Virtex™-4r

Specifications of XC4VLX60-11FFG668C

Package

668FCBGA

Family Name

Virtex®-4

Device Logic Units

59904

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

448

Ram Bits

2949120

Number Of Logic Elements/cells

59904

Number Of Labs/clbs

6656

Total Ram Bits

2949120

Number Of I /o

448

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

668-BBGA, FCBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

HW-AFX-FF668-400 - BOARD DEV VIRTEX 4 FF668

Number Of Gates

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1496

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC4VLX60-11FFG668C

Manufacturer:

Xilinx Inc

Quantity:

10 000

Configuration Switching Characteristics

Table 43: Configuration Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

Power-up Timing Characteristics

Master/Slave Serial Mode Programming Switching

SelectMAP Mode Programming Switching

T

T

T

T

T

T

T

T

T

T

F

F

F

T

T

T

T

F

F

F

F

T

CONFIG

PL

POR

ICCK

PROGRAM

DCC

DSCK

CCO

CCH

CCL

CC_SERIAL

MAX_SLAVE

MCCTOL

SMDCC

SMCSCC

SMCCW

SMCKBY

CC_SELECTMAP

MAX_SELECTMAP

MAX_READBACK

MCCTOL

SMCO

/

T

/

T

CCD

(1,2)

/

/

SCKD

T

/

T

T

SMCCD

SMWCC

SMCCCS

/

F

Symbol

MAX_ICAP

Maximum time to configure device after

V

Program Latency

Power-on-Reset

CCLK (output) delay

Program Pulse Width

DIN Setup/Hold, slave mode

DIN Setup/Hold, master mode

DOUT

High Time

Low Time

Maximum Frequency, master mode with

respect to nominal CCLK.

Maximum Frequency, slave mode external

CCLK

Frequency Tolerance, master mode with

respect to nominal CCLK.

SelectMAP Data Setup/Hold

CS_B Setup/Hold

RDWR_B Setup/Hold

BUSY Propagation Delay

Maximum Frequency, master mode with

respect to nominal CCLK.

Maximum Configuration Frequency, slave

mode external CCLK

Maximum Readback Frequency

Frequency Tolerance, master mode with

respect to nominal CCLK.

SelectMAP Readback Clock-to-Out

CCINT

has been applied.

www.xilinx.com

Description

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

T

PL

±50

±50

-12

500

300

100

100

100

100

0.5

0.5

1.0

0.5

1.0

7.5

2.0

2.0

2.0

0.0

1.0

0.5

6.0

1.0

8.0

8.0

10

80

+ 10 T

Speed Grade

PL

±50

±50

-11

500

300

100

100

100

100

0.5

0.5

1.0

0.5

1.0

7.5

2.0

2.0

2.0

0.0

1.0

0.5

6.0

1.0

8.0

8.0

10

80

+ 10 T

PL

±50

±50

-10

500

300

100

100

100

100

0.5

0.5

1.0

0.5

1.0

7.5

2.0

2.0

2.0

0.0

1.0

0.5

6.0

1.0

8.0

8.0

10

80

+ 10

MHz, Max

MHz, Max

MHz, Max

MHz, Max

MHz, Max

µs/frame,

ms, Max

minutes

ns, Max

ns, Max

ns, Max

ns, Min

ns, Min

ns, Min

ns, Min

ns, Min

ns, Min

ns, Min

ns, Min

ns, Min

Units

Max

%

%

36