SL72A8M64M8M-C75EWU STEC, SL72A8M64M8M-C75EWU Datasheet

SL72A8M64M8M-C75EWU

Specifications of SL72A8M64M8M-C75EWU

Related parts for SL72A8M64M8M-C75EWU

SL72A8M64M8M-C75EWU Summary of contents

Page 1

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) GENERAL DESCRIPTION The SL72A8M64M8M-C75xW( 64M x 72 bit Double Data Rate (DDR) Synchronous Dynamic RAM (SDRAM) Small- Outline Dual In-line Memory Module (SO-DIMM). The module consists of nine CMOS 16M x 8 bit x 4 bank DDR SDRAMs in 66-pin 400-mil TSOP II packages mounted on a 200-pin glass epoxy substrate ...

Page 2

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) PIN CONFIGURATION (* = Not Used Active Low) Pinout Pin Front Pin Back Pin REF REF DQS \DQS DQS \DQS / DQS \DQS Pin Description Pin Symbol Pin Function CK Clock inputs, positive line (0:2) /CK Clock inputs, negative line ...

Page 3

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) FUNCTIONAL BLOCK DIAGRAM / 0-7 / DQS DQS \DQS 8-15 / DQS DQS \DQS 16- DQS DQS \DQS 24- DQS DQS \DQS 0 DQS DQS \DQS /AP /AP SDRAMs U0- SDRAMs U0- /RAS: SDRAMs U0-U8 /RAS /CAS: SDRAMs U0-U8 ...

Page 4

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) SERIAL PRESENCE DETECT INFORMATION 2 Serial PD Interface Protocol Current sink capability of SDA driver <=3mA; Maximum clock frequency: 100 KHz Byte # Function Described bytes written into serial memory at module manufacturer 1 Total # of bytes of SPD memory device ...

Page 5

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) SERIAL PRESENCE DETECT INFORMATION Byte # Function Described 36-40 Superset information (may be used in future) 41 Row cycle time ( Auto refresh cycle time (t RFC 43 Maximum SDRAM device cycle time (t 44 DQS-DQ skew (t ) DQSQ 45 SDRAM device data hold skew factor (t ...

Page 6

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) ABSOLUTE MAXIMUM RATINGS Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional Operation should be restricted to recommended operating condition. Exposure to higher than recommended voltage for extended periods of time may affect device reliability. ...

Page 7

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) DC CHARACTERISTICS (Recommended operating conditions unless otherwise noted; Module IDD was calculated on the basis of component IDD and can be differently measured according to DQ loading cap.) Parameter/Condition OPERATING CURRENT: One bank; Active-Precharge (MIN (MIN); DQ, DM and DQS inputs changing once per clock cyle ...

Page 8

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) AC OPERATING TEST CONDITIONS (V =V Q=2.5V, T =0°C to 70° Parameter Input reference voltage for Clock Input signal maximum peak swing Input signal minimum slew rate Input levels ( Input timing measurement ref. level Output timing measurement ref ...

Page 9

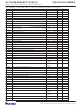

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) AC TIMING PARAMETERS Symbol Parameter tRC Row cycle time t RFC Refresh row cycle time tRAS Row active time tRCD /RAS to /CAS delay tRP Row precharge time tRRD Row active to Row acitve delay tWR ...

Page 10

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) Notes: 1. Maximum burst refresh The specific requirement is that DQS be valid(High or Low before this CK edge. The case shown(DQS going from High_Z to logic Low) applies when no writes were previously in progress on the bus previous write was in progress, DQS could be High at this time, depending on tDQSS ...

Page 11

... SL72A8M64M8M-C75xW(U) (Where x = CAS Latency; U selects RoHS Compliant, lead-free version.) REVISION HISTORY Rev. Change Description from Previous Revision -103 03/24/2004. Component-based specs added. -104 03/25/2004. Board updated from PCB 955 (1.400") to PCB 1195 (1.250"). -105 04/12/2004. CK1 and CK2 termination removed from block ...