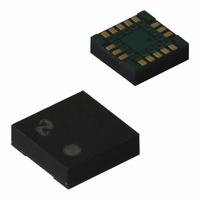

LMX2335USLBX National Semiconductor, LMX2335USLBX Datasheet - Page 33

LMX2335USLBX

Manufacturer Part Number

LMX2335USLBX

Description

IC FREQ SYNTH DUAL 16LAMINATECSP

Manufacturer

National Semiconductor

Series

PLLatinum™r

Type

PLL Frequency Synthesizerr

Datasheet

1.LMX2335UTMNOPB.pdf

(48 pages)

Specifications of LMX2335USLBX

Pll

Yes with Bypass

Input

CMOS, TTL

Output

CMOS

Number Of Circuits

1

Ratio - Input:output

3:1

Differential - Input:output

No/No

Frequency - Max

1.2GHz

Divider/multiplier

Yes/No

Voltage - Supply

2.7 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

16-Laminate CSP

Frequency-max

1.2GHz

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

LMX2335USLBXTR

1.0 Functional Description

The basic phase-lock-loop (PLL) configuration consists of a

high-stability crystal reference oscillator, a frequency synthe-

sizer such as the National Semiconductor LMX2335U or

LMX2336U, a voltage controlled oscillator (VCO), and a

passive loop filter. The frequency synthesizer includes a

phase detector, current mode charge pump, programmable

reference R and feedback N frequency dividers. The VCO

frequency is established by dividing the crystal reference

signal down via the reference divider to obtain a comparison

reference frequency. This reference signal, F

sented to the input of a phase/frequency detector and com-

pared with the feedback signal, F

dividing the VCO frequency down by way of the feedback

divider. The phase/frequency detector measures the phase

error between the F

signals that are directly proportional to the phase error. The

charge pump then pumps charge into or out of the loop filter

based on the magnitude and direction of the phase error.

The loop filter converts the charge into a stable control

voltage for the VCO. The phase/frequency detector’s func-

tion is to adjust the voltage presented to the VCO until the

feedback signal’s frequency and phase match that of the

reference signal. When this “Phase-Locked” condition exists,

the VCO frequency will be N times that of the comparison

frequency, where N is the feedback divider ratio.

1.1 REFERENCE OSCILLATOR INPUT

The reference oscillator frequency for both the RF1 and RF2

PLLs is provided from an external reference via the OSC

pin. The reference buffer circuit supports input frequencies

from 5 to 40 MHz with a minimum input sensitivity of 0.5 V

The reference buffer circuit has an approximate V

threshold and can be driven from an external CMOS or TTL

logic gate. Typically, the OSC

of a crystal oscillator.

1.2 REFERENCE DIVIDERS (R COUNTERS)

The reference dividers divide the reference input signal,

OSC

circuits feeds the reference input of the phase detector. This

reference input to the phase detector is often referred to as

the comparison frequency. The divide ratio should be chosen

such that the maximum phase comparison frequency (F

or F

The RF1 and RF2 reference dividers are each comprised of

15-bit CMOS binary counters that support a continuous in-

teger divide ratio from 3 to 32767. The RF1 and RF2 refer-

ence divider circuits are clocked by the output of the refer-

ence buffer circuit which is common to both.

1.3 PRESCALERS

The f

LMX2336U device drives the input of a bipolar, differential-

pair amplifier. The output of the bipolar, differential-pair am-

plifier drives a chain of ECL D-type flip-flops in a dual modu-

φRF2

in

IN

, by a factor of R. The output of the reference divider

RF1 (f

) of 10 MHz is not exceeded.

IN

RF2) and f

r

and F

IN

in

p

RF1 (f

pin is connected to the output

signals and outputs control

p

, which was obtained by

IN

RF2) input pins of the

r

, is then pre-

CC

/2 input

φRF1

PP

in

.

33

lus configuration. The output of the prescaler is used to clock

the subsequent feedback dividers. The complementary in-

puts of both the RF1 and RF2 synthesizers can be driven

differentially, or the negative input can be AC coupled to

ground through an external capacitor for single ended con-

figuration. A 64/65 or a 128/129 prescale ratio can be se-

lected for the both the RF1 and RF2 synthesizers. On the

other hand, the LMX2335U PLL is only intended for single

ended operation. Similarly, a 64/65 or a 128/129 prescale

ratio can be selected for both the RF1 and RF2 synthesizers.

1.4 PROGRAMMABLE FEEDBACK DIVIDERS (N

COUNTERS)

The programmable feedback dividers operate in concert with

the prescalers to divide the input signal f

The output of the programmable reference divider is pro-

vided to the feedback input of the phase detector circuit. The

divide ratio should be chosen such that the maximum phase

comparison frequency (F

exceeded.

The programmable feedback divider circuit is comprised of

an A counter (swallow counter) and a B counter (program-

mble binary counter). The RF1 N_CNTRA counter and RF2

N_CNTRA counter are both 7-bit CMOS swallow counters,

programmable from 0 to 127. The RF1 N_CNTRB and RF2

N_CNTRB counters are both 11-bit CMOS binary counters,

programmable from 3 to 2047. A continuous integer divide

ratio is achieved if N ≥ P

prescaler selected. Divide ratios less than the minimum con-

tinuous divide ratio are achievable as long as the binary

programmable counter value is greater than the swallow

counter value (N_CNTRB ≥ N_CNTRA). Refer to Sections

2.5.1, 2.5.2, 2.7.1 and 2.7.2 for details on how to program

the N_CNTRA and N_CNTRB counters. The following equa-

tions are useful in determining and programming a particular

value of N:

N = (P x N_CNTRB) + N_CNTRA

f

Definitions:

IN

F

f

N_CNTRA: RF1 or RF2 A counter value

N_CNTRB: RF1 or RF2 B counter value

P:

IN

= N x F

φ

:

:

φ

RF1 or RF2 phase detector comparison

frequency

RF1 or RF2 input frequency

Preset

prescaler

LMX2335U RF1 synthesizer: P = 64 or 128

LMX2336U RF1 synthesizer: P = 64 or 128

LMX2335U RF2 synthesizer: P = 64 or 128

LMX2336U RF2 synthesizer: P = 64 or 128

modulus

*

φRF1

(P−1), where P is the value of the

or F

of

φRF2

the

) of 10 MHz is not

IN

by a factor of N.

dual

www.national.com

moduIus