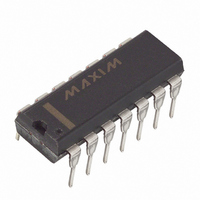

DS1868-100+ Maxim Integrated Products, DS1868-100+ Datasheet - Page 5

DS1868-100+

Manufacturer Part Number

DS1868-100+

Description

IC POT DIGITAL DUAL 100K 14-DIP

Manufacturer

Maxim Integrated Products

Datasheet

1.DS1868-10.pdf

(14 pages)

Specifications of DS1868-100+

Taps

256

Resistance (ohms)

100K

Number Of Circuits

2

Temperature Coefficient

750 ppm/°C Typical

Memory Type

Volatile

Interface

3-Wire Serial

Voltage - Supply

2.7 V ~ 3.3 V, 4.5 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Package / Case

14-DIP (0.300", 7.62mm)

Resistance In Ohms

100K

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

DS1868

STACKED CONFIGURATION Figure 3

CASCADE OPERATION

A feature of the DS1868 is the ability to control multiple devices from a single processor. Multiple

DS1868s can be linked or daisy chained as shown in Figure 4. As a data bit is entered into the I/O shift

register of the DS1868 a bit will appear at the C

output after a minimum delay of 50 nanoseconds. The

OUT

stack select bit of the DS1868 will always be the first out the part at the beginning of a transaction. The

C

pin will always have the value of the stack select bit (b0) when

is inactive.

RST

OUT

CASCADING MULTIPLE DEVICES Figure 4

The C

output of the DS1868 can be used to drive the DQ input of another DS1868. When connecting

OUT

multiple devices, the total number of bits transmitted is always 17 times the number of DS1868s in the

daisy chain.

An optional feedback resistor can be placed between the C

terminal of the last device and the first

OUT

DS1868 DQ, input thus allowing the controlling processor to read, as well as, write data, or circularly

clock data through the daisy chain. The value of the feedback or isolation resistor should be in the range

from 2 to 10 kohms.

When reading data via the C

pin and isolation resistor, the DQ line is left floating by the reading

OUT

device. When

is driven high, bit 17 is present on the C

pin, which is fed back to the input DQ

RST

OUT

pin through the isolation resistor. When the CLK input transitions low to high, bit 17 is loaded into the

first position of the I/O shift register and bit 16 becomes present on C

and DQ of the next device. After

OUT

17 bits (or 17 times the number of DS1868s in the daisy chain), the data has shifted completely around

and back to its original position. When

transitions to the low state to end data transfer, the value (the

RST

same as before the read occurred) is loaded into the wiper-0, wiper-1, and stack select bit I/O register.

5 of 14