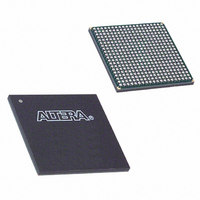

EP1C4F400C8N Altera, EP1C4F400C8N Datasheet - Page 56

EP1C4F400C8N

Manufacturer Part Number

EP1C4F400C8N

Description

IC CYCLONE FPGA 4K LE 400-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C4F400C8N

Number Of Logic Elements/cells

4000

Number Of Labs/clbs

400

Total Ram Bits

78336

Number Of I /o

301

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

400-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1806

EP1C4F400C8N

EP1C4F400C8N

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C4F400C8N

Manufacturer:

CYCLONE

Quantity:

5 510

Company:

Part Number:

EP1C4F400C8N

Manufacturer:

ALTERA

Quantity:

104

Part Number:

EP1C4F400C8N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP1C4F400C8NAA

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP1C4F400C8NAB

Manufacturer:

ALTERA

Quantity:

3 000

Cyclone Device Handbook, Volume 1

2–50

Preliminary

of the standard. Using minimum settings provides signal slew rate

control to reduce system noise and signal overshoot.

possible settings for the I/O standards with drive strength control.

Open-Drain Output

Cyclone devices provide an optional open-drain (equivalent to an

open-collector) output for each I/O pin. This open-drain output enables

the device to provide system-level control signals (e.g., interrupt and

write-enable signals) that can be asserted by any of several devices.

Notes to

(1)

(2)

LVTTL (3.3 V)

LVCMOS (3.3 V)

LVTTL (2.5 V)

LVTTL (1.8 V)

LVCMOS (1.5 V)

Table 2–11. Programmable Drive Strength

SSTL-3 class I and II, SSTL-2 class I and II, and 3.3-V PCI I/O Standards do not

support programmable drive strength.

This is the default current strength setting in the Quartus II software.

Table

I/O Standard

2–11:

I

OH

/I

OL

Note (1)

Current Strength Setting (mA)

Table 2–11

24(2)

12(2)

16(2)

12(2)

8(2)

12

16

12

4

8

2

4

8

2

8

2

8

2

4

Altera Corporation

shows the

May 2008