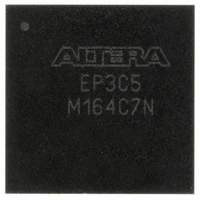

EP3C5M164C7N Altera, EP3C5M164C7N Datasheet - Page 58

EP3C5M164C7N

Manufacturer Part Number

EP3C5M164C7N

Description

IC CYCLONE III FPGA 5K 164 MBGA

Manufacturer

Altera

Series

Cyclone® IIIr

Datasheets

1.EP3C5F256C8N.pdf

(5 pages)

2.EP3C5F256C8N.pdf

(34 pages)

3.EP3C5F256C8N.pdf

(66 pages)

4.EP3C5F256C8N.pdf

(14 pages)

5.EP3C5F256C8N.pdf

(76 pages)

6.EP3C5M164C7N.pdf

(274 pages)

Specifications of EP3C5M164C7N

Number Of Logic Elements/cells

5136

Number Of Labs/clbs

321

Total Ram Bits

423936

Number Of I /o

106

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

164-MBGA

Family Name

Cyclone III

Number Of Logic Blocks/elements

5136

# I/os (max)

106

Frequency (max)

437.5MHz

Process Technology

65nm

Operating Supply Voltage (typ)

1.2V

Logic Cells

5136

Ram Bits

423936

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

164

Package Type

MBGA

For Use With

544-2601 - KIT DEV CYCLONE III LS EP3CLS200544-2411 - KIT DEV NIOS II CYCLONE III ED.

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2559

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP3C5M164C7N

Manufacturer:

ALTERA

Quantity:

526

Page 58

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

Quick Design Debugging Using SignalProbe chapter in volume 3 of the Quartus II

Handbook

Design Debugging Using the SignalTap II Embedded Logic Analyzer chapter in volume

3 of the Quartus II Handbook

In-System Debugging Using External Logic Analyzers chapter in volume 3 of the

Quartus II Handbook

In-System Updating of Memory and Constants chapter in volume 3 of the Quartus II

Handbook

Design Debugging Using In-System Sources and Probes chapter in volume 3 of the

Quartus II Handbook

sld_virtual_jtag Megafunction User Guide

AN 447: Interfacing Cyclone III Devices with 3.3/3.0/2.5 V LVTTL/LVCMOS I/O

Systems

I/O Management chapter in volume 2 of the Quartus II Handbook

AN 508: Cyclone III Simultaneous Switching Noise (SSN) Design Guidelines

AN 224: High-Speed Board Layout Guidelines

AN 315: Guidelines for Designing High-Speed FPGA PCBs

Signal Integrity Analysis with Third-Party Tools chapter in volume 3 of the Quartus II

Handbook

Cyclone III Device Family Pin Connection Guidelines

Hot Socketing and Power-On Reset in Cyclone III Devices chapter in volume 1 of the

Cyclone III Device Handbook

JTAG Configuration and ISP Troubleshooter

FPGA Configuration Troubleshooter

Recommended HDL Coding Styles chapter in volume 1 of the Quartus II Handbook

Synthesis in volume 1 of the Quartus II Handbook

Volume 4: SOPC Builder of the Quartus II Handbook

Design Recommendations for Altera Devices and the Quartus II Design Assistant

chapter in volume 1 of the Quartus II Handbook

altclkctrl Megafunction User Guide

altpll Megafunction User Guide

Incremental Compilation for Hierarchical and Team-Based Design chapter in volume 1

of the Quartus II Handbook

Analyzing and Optimizing the Design Floorplan chapter in volume 2 of the Quartus II

Handbook

Power Optimization chapter in volume 2 of the Quartus II Handbook

Design Space Explorer chapter in volume 2 of the Quartus II Handbook

Quartus II Classic Timing Analyzer chapter of the Quartus II Handbook

Software Settings section in volume 2 of the Configuration Handbook

© November 2008 Altera Corporation

Referenced Documents