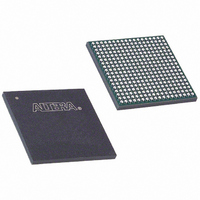

EP1C4F324I7 Altera, EP1C4F324I7 Datasheet - Page 34

EP1C4F324I7

Manufacturer Part Number

EP1C4F324I7

Description

IC CYCLONE FPGA 4K LE 324-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C4F324I7

Number Of Logic Elements/cells

4000

Number Of Labs/clbs

400

Total Ram Bits

78336

Number Of I /o

249

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

324-FBGA

Family Name

Cyclone®

Number Of Logic Blocks/elements

4000

# I/os (max)

249

Frequency (max)

320.1MHz

Process Technology

0.13um (CMOS)

Operating Supply Voltage (typ)

1.5V

Logic Cells

4000

Ram Bits

78336

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

324

Package Type

FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-1045

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C4F324I7

Manufacturer:

ALTERA41

Quantity:

742

Part Number:

EP1C4F324I7

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP1C4F324I7N

Manufacturer:

ALTERA

Quantity:

996

Part Number:

EP1C4F324I7N

Manufacturer:

ALTERA

Quantity:

20 000

Cyclone Device Handbook, Volume 1

Figure 2–20. Read/Write Clock Mode in Simple Dual-Port Mode

Notes to

(1)

(2)

2–28

Preliminary

wraddress[ ]

address[ ]

byteena[ ]

wrclken

wrclock

rdclken

rdclock

All registers shown except the rden register have asynchronous clear ports.

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both

read and write operations.

data[ ]

wren

rden

Figure

6 LAB Row

Clocks

6

2–20:

Read/Write Clock Mode

The M4K memory blocks implement read/write clock mode for simple

dual-port memory. You can use up to two clocks in this mode. The write

clock controls the block's data inputs, wraddress, and wren. The read

clock controls the data output, rdaddress, and rden. The memory

blocks support independent clock enables for each clock and

asynchronous clear signals for the read- and write-side registers.

Figure 2–20

D

ENA

D

ENA

D

ENA

D

ENA

D

ENA

D

ENA

shows a memory block in read/write clock mode.

Q

Q

Q

Q

Q

Q

Generator

Pulse

Write

Data In

Read Address

Write Address

Byte Enable

Read Enable

Write Enable

Notes

Memory Block

1,024 × 4

2,048 × 2

4,096 × 1

Data Out

256 × 16

512 × 8

(1),

(2)

D

ENA

Q

Altera Corporation

To MultiTrack

Interconnect

May 2008