EP1S25F672C8 Altera, EP1S25F672C8 Datasheet - Page 5

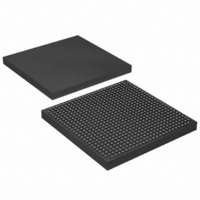

EP1S25F672C8

Manufacturer Part Number

EP1S25F672C8

Description

IC STRATIX FPGA 25K LE 672-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S25F672C8

Number Of Logic Elements/cells

25660

Number Of Labs/clbs

2566

Total Ram Bits

1944576

Number Of I /o

473

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1119

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1S25F672C8

Manufacturer:

AD

Quantity:

2 562

Company:

Part Number:

EP1S25F672C8

Manufacturer:

ALTERA

Quantity:

3 000

Part Number:

EP1S25F672C8

Manufacturer:

ALTERA

Quantity:

20 000

Company:

Part Number:

EP1S25F672C8N

Manufacturer:

ALTERA

Quantity:

465

Part Number:

EP1S25F672C8N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

Chapter

4

Date/Version

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

Table 4–48 on page

and updated symbol names.

Updated power-up current (ICCINT) required to power a Stratix

device on

Updated

page

Table 4–49 on page

t

updated symbol names.

Table 4–50 on page

t

t

Table 4–52 on page

column, and added rows t

Table 4–52 on page

column, and added rows t

Table 4–53 on page

t

Updated Note 2 in

Table 4–54 on page

column, and added rows t

Updated Note 2 in

Deleted Note 2 from

page

Updated

page

Added Note 4 to

Deleted Note 1 from

page

Added new section

page

Deleted Note 1 from

page

Deleted Note 2 from

page

Added Note 4 to

Table 4–102 on page

Updated description of

page

Added Note 1 to

page

Updated

page

Deleted Note 2 from

on page

Added new paragraph about output adder delays on

Updated

Added Note 1 to

M4KBESU

MRAMBESU

MRAMRADDRH

ZXPLL

.

4–27.

4–41.

4–56. Added rows T

4–50.

4–60.

4–50.

4–56.

4–66.

4–74.

4–74.

, and t

4–69.

Table 4–37 on page 4–22

Table 4–55 on page 4–36

Table 4–103 on page 4–66

Table 4–110 on page

, and t

page

, and updated symbol names.

M4KBEH,

4–17.

MRAMBEH

Table 4–101 on page

Table 4–101 on page

Table 4–109 on page 4–73

Table 4–111

Table 4–53 on page

Table 4–54 on page

“I/O Timing Measurement Methodology” on

4–30: added rows t

Table 4–55 on page 4–36

Table 4–67 on page 4–42

Table 4–67 on page 4–42

Table 4–85 on page 4–51

Table 4–103 on page 4–66

4–31: added rows t

4–31: added rows t

4–34: updated table, deleted “Conditions”

4–34: updated table, deleted “Conditions”

4–34: updated table and added rows t

4–35: updated table, deleted “Conditions”

deleted rows t

4–64: updated table and added Note 4.

“External I/O Delay Parameters” on

, deleted rows t

Changes Made

XZ

XZ

XZPLL

XZ

, T

and t

and t

through

ZX

4–74.

and t

, T

ZX

ZX

Stratix Device Family Data Sheet

through

through

XZPLL

M4KRADDRASU

.

.

ZXPLL

through

Table 4–113 on page

4–62.

4–62.

M512CLKSENSU

MRAMADDRASU

4–34.

4–35.

M4KCLKENSU

MRAMCLKENSU

, and T

.

Table 4–43 on

Table 4–96 on

and

Table 4–110 on

through

through

through

through

ZXPLL.

through

and t

Table 4–110 on

, t

and t

, t

M4KCLKENH

and

page

M4KRADDRH

MRAMCLKENH

Table 4–66 on

Table 4–84 on

Table 4–84 on

Table 4–96 on

Table 4–106

M512CLKENH

Section I–5

4–68.

XZPLL

4–75.

,

, and

and

,

,