CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet

CY7C68014A-56BAXC

Specifications of CY7C68014A-56BAXC

Available stocks

Related parts for CY7C68014A-56BAXC

CY7C68014A-56BAXC Summary of contents

Page 1

... Engine “Soft Configuration” FIFO and endpoint memory Easy firmware changes (master or slave operation) Figure 1-1. Block Diagram • 198 Champion Court • San Jose CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 2 C controller, runs at 100 or 400 kHz Master Abundant I/O Additional I/Os (24) including two USARTS ...

Page 2

... Features (CY7C68013A/14A only) • CY7C68014A: Ideal for battery powered applications — Suspend current: 100 ∝A (typ) • CY7C68013A: Ideal for non-battery powered applica- tions — Suspend current: 300 ∝A (typ) • Available in five lead-free packages with GPIOs — 128-pin TQFP (40 GPIOs), 100-pin TQFP (40 GPIOs), ...

Page 3

... Note: 1. 115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a “1” for UART0 and/or UART1, respectively. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A The CLKOUT pin, which can be three-stated and inverted using internal control bits, outputs the 50% duty cycle 8051 clock, at the selected 8051 clock frequency— ...

Page 4

... Two control bits in the USBCS (USB Control and Status) register control the ReNumeration process: DISCON and Note The I C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Ax Bx IOC IOD INT2CLR IOE ...

Page 5

... INT2VEC byte at 0x0045 will direct the jump to the correct address out of the 27 addresses within the page. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A USB INTERRUPT TABLE FOR INT2 Source Set-up Data Available ...

Page 6

... RESET# pin is asserted. Cypress provides an application note which describes and recommends power on reset implementation and can be found on the Cypress web site. For more information on reset imple- mentation for the FX2 family of products visit the http://www.cypress.com. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Notes [3] . Figure 3-2 Page ...

Page 7

... External logic asserts the PA3/WU2 pin. The second wakeup pin, WU2, can also be configured as a general purpose I/O pin. This allows a simple external R-C network to be used as a periodic wakeup source. Note that WAKEUP is by default active LOW. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A RESET 3.3V 3 ...

Page 8

... Memory (RD#,WR#) (Ok to populate 16 KBytes data memory RAM here—RD#/WR# Data strobes are not (RD#,WR#)* active) Data 2 C interface boot access Figure 3-4. External Code Memory CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 48 KBytes External Code Memory (PSEN#) Code 64 KBytes External Code Memory (PSEN#) Code Page ...

Page 9

... Eight 512-byte buffers, bulk, interrupt, or isochronous. EP4 and EP8 can be double buffered, while EP2 and 6 can be either double, triple, or quad buffered. For high-speed end- point configuration options, see Figure 3-5. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A FFFF 4 KBytes EP2-EP8 buffers (8 x 512) ...

Page 10

... CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A ...

Page 11

... GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 32 transactions. Page ...

Page 12

... EZ-USB FX2 to EZ-USB FX2LP, please see further details in the application note titled Migrating from EZ-USB FX2 to EZ-USB FX2LP, which is available on the Cypress Website. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 2 C port that is driven by two internal C port operates in master mode only. ...

Page 13

... CY7C68013-128AC CY7C68013A-128AXC or CY7C68014A-128AXC 3.20 CY7C68013A/14A and CY7C68015A/16A Differences CY7C68013A is identical to CY7C68014A in form, fit, and functionality. CY7C68015A is identical to CY7C68016A in form, fit, and functionality. CY7C68014A and CY7C68016A have a lower suspend current than CY7C68013A and CY7C68015A respectively. CY7C68014A and CY7C68016A have a lower suspend current than CY7C68013A and ...

Page 14

... Port mode is the power-on default configuration. The 100-pin package adds functionality to the 56-pin package by adding these pins: • PORTC or alternate GPIFADR[7:0] address signals Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A • PORTE or alternate GPIFADR[8] address signal and seven additional 8051 signals • Three GPIF Control signals • ...

Page 15

... WR# CS# OE# PSEN# A15 A14 A13 A12 A11 A10 128 Figure 4-1. Signals ** pinout for CY7C68015A/CY7C68016A only CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Slave FIFO FD[15] FD[14] FD[13] FD[12] FD[11] FD[10] FD[9] FD[8] FD[7] FD[6] FD[5] FD[4] FD[3] FD[2] FD[1] FD[0] SLRD SLWR FLAGA FLAGB FLAGC ...

Page 16

... A14 A15 25 VCC 26 27 GND 28 INT4 *IFCLK 32 RESERVED 33 BKPT SCL SDA 37 38 OE# Figure 4-2. CY7C68013A/CY7C68014A 128-pin TQFP Pin Assignment Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A CY7C68013A/CY7C68014A 128-pin TQFP * denotes programmable polarity 102 PD0/FD8 101 *WAKEUP 100 VCC 99 RESET# 98 CTL5 GND 92 PA7/*FLAGD/SLCS# ...

Page 17

... DMINUS 18 AGND 19 VCC 20 GND 21 INT4 *IFCLK 26 RESERVED 27 BKPT 28 SCL 29 SDA 30 Figure 4-3. CY7C68013A/CY7C68014A 100-pin TQFP Pin Assignment Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A CY7C68013A/CY7C68014A 100-pin TQFP * denotes programmable polarity PD0/FD8 80 *WAKEUP 79 VCC 78 RESET# 77 CTL5 76 GND 75 PA7/*FLAGD/SLCS# 74 PA6/*PKTEND 73 PA5/FIFOADR1 72 PA4/FIFOADR0 71 PA3/*WU2 ...

Page 18

... Figure 4-4. CY7C68013A/CY7C68014A 56-pin SSOP Pin Assignment Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A 56-pin SSOP PD5/FD13 1 PD6/FD14 2 PD7/FD15 3 GND 4 CLKOUT/T1OUT 5 VCC 6 GND 7 RDY0/*SLRD 8 RDY1/*SLWR 9 AVCC PA7/*FLAGD/SLCS# 10 XTALOUT PA6/PKTEND 11 XTALIN PA5/FIFOADR1 12 AGND PA4/FIFOADR0 13 AVCC 14 DPLUS PA2/*SLOE 15 DMINUS PA1/INT1# 16 AGND PA0/INT0# ...

Page 19

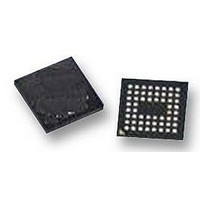

... DPLUS 8 DMINUS 9 AGND 10 VCC 11 GND 12 *IFCLK/**PE0/T0OUT 13 RESERVED 14 Figure 4-5. CY7C68013A/14A/15A/16A 56-pin QFN Pin Assignment Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A CY7C68013A/CY7C68014A & CY7C68015A/CY7C68016A 56-pin QFN * denotes programmable polarity ** denotes CY7C68015A/CY7C68016A pinout RESET# 42 GND 41 PA7/*FLAGD/SLCS# 40 PA6/*PKTEND 39 PA5/FIFOADR1 38 PA4/FIFOADR0 37 PA3/*WU2 ...

Page 20

... Figure 4-6. CY7C68013A 56-pin VFBGA Pin Assignment - Top view Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Page ...

Page 21

... I/O/Z Z I/O/Z Z I/O/Z Z I/O/Z Z Output H Program Store Enable. This active-LOW signal indicates an 8051 code fetch from external memory active for program memory fetches from 0x4000–0xFFFF when the EA pin is LOW, or from 0x0000–0xFFFF when the EA pin is HIGH. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 22

... I/O/Z I Multiplexed pin whose function is selected by: (PA1) PORTACFG.1 PA1 is a bidirectional IO port pin. INT1# is the active-LOW 8051 INT1 interrupt input signal, which is either edge triggered (IT1 = 1) or level triggered (IT1 = 0). CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 23

... IFCONFIG[1..0]. PB2 is a bidirectional I/O port pin. FD[2] is the bidirectional FIFO/GPIF data bus. I/O/Z I Multiplexed pin whose function is selected by the (PB3) following bits: IFCONFIG[1..0]. PB3 is a bidirectional I/O port pin. FD[3] is the bidirectional FIFO/GPIF data bus. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 24

... Multiplexed pin whose function is selected by (PC7) PORTCCFG.7 PC7 is a bidirectional I/O port pin. GPIFADR7 is a GPIF address output pin. I/O/Z I Multiplexed pin whose function is selected by the (PD0) IFCONFIG[1..0] and EPxFIFOCFG.0 (wordwide) bits. FD[8] is the bidirectional FIFO/GPIF data bus. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 25

... Multiplexed pin whose function is selected by the (PE3) PORTECFG.3 bit. PE3 is a bidirectional I/O port pin. RXD0OUT is an active-HIGH signal from 8051 UART0. If RXD0OUT is selected and UART0 is in Mode 0, this pin provides the output data for UART0 only when sync mode. Otherwise CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 26

... RDY5 is a GPIF input signal. O/Z H Multiplexed pin whose function is selected by the following bits: IFCONFIG[1..0]. CTL0 is a GPIF control output. FLAGA is a programmable slave-FIFO output status flag signal. Defaults to programmable for the FIFO selected by the FIFOADR[1:0] pins. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 27

... Input N/A RXD1is an active-HIGH input signal for 8051 UART1, which provides data to the UART in all modes. Output H TXD1is an active-HIGH output pin from 8051 UART1, which provides the output clock in sync mode, and the output data in async mode. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description Page ...

Page 28

... Ground. N/A N/A No Connect. This pin must be left open. N/A N/A No Connect. This pin must be left open. N/A N/A No Connect. This pin must be left open. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Description chip from suspending interface. Connect to VCC with a 2. peripheral is attached. 2 C-compatible interface. Connect to VCC ...

Page 29

... LINE15 LINE14 LINE13 LINE12 LINE11 LINE7 LINE6 LINE5 LINE4 LINE3 COL5 COL4 COL3 COL2 COL1 LINE15 LINE14 LINE13 LINE12 LINE11 CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default xxxxxxxx RW reserved reserved reserved 00000000 R CLKINV CLKOE 8051RES 00000010 rrbbbbbr GSTATE IFCFG1 IFCFG0 10000000 RW FLAGA2 FLAGA1 FLAGA0 00000000 RW ...

Page 30

... URES SUSP 0 EP0ACK HSGRANT URES SUSP EP8 EP6 EP4 EP2 EP1OUT EP8 EP6 EP4 EP2 EP1OUT CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default LINE2 LINE1 LINE0 00000000 R COL0 0 0 00000000 R 0 PFC9 PFC8 10001000 bbbbbrbb PFC9 IN:PKTS[2] 10001000 bbbbbrbb OUT:PFC8 PFC2 PFC1 PFC0 00000000 RW PFC2 ...

Page 31

... BC6 BC5 BC4 BC3 BC6 BC5 BC4 BC3 HSNAK NPAK2 NPAK1 NPAK0 FULL CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default 0 0 ERRLIMIT 00000000 ERRLIMIT 0000000x bbbbrrrb LIMIT2 LIMIT1 LIMIT0 xxxx0100 rrrrbbbb xxxxxxxx W I2V0 0 0 00000000 R I4V0 0 0 10000000 R 0 INT4SRC AV4EN 00000000 RW 0 INT1 INT0 ...

Page 32

... RDYASYNC CTLTOGL SUSTAIN TC31 TC30 TC29 TC28 TC27 TC23 TC22 TC21 TC20 TC19 TC15 TC14 TC13 TC12 TC11 TC7 TC6 TC5 TC4 TC3 CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default EMPTY 0 STALL 00101000 rrrrrrrb EMPTY 0 STALL 00000100 rrrrrrrb EMPTY 0 STALL 00000100 rrrrrrrb 00000010 00000010 00000110 ...

Page 33

... DISCON A15 A14 A13 A12 A11 A15 A14 A13 A12 A11 SMOD0 CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default 0 FS1 FS0 00000000 FIFO2FLAG 00000000 xxxxxxxx W 0 FS1 FS0 00000000 FIFO4FLAG 00000000 xxxxxxxx W 0 FS1 FS0 00000000 FIFO6FLAG 00000000 xxxxxxxx W 0 FS1 FS0 00000000 FIFO8FLAG 00000000 RW ...

Page 34

... D12 D11 SM0_1 SM1_1 SM2_1 REN_1 TB8_1 TF2 EXF2 RCLK TCLK EXEN2 D15 D14 D13 D12 D11 CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default IT1 IE0 IT0 00000000 00000000 00000000 00000000 RW D10 D9 D8 00000000 RW D10 D9 D8 00000000 RW MD2 MD1 MD0 00000001 xxxxxxxx 00001000 RW A10 A9 A8 ...

Page 35

... Document #: 38-08032 Rev RS1 RS0 1 ERESI RESI INT6 EX6 EX5 PX6 PX5 CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Default 00000000 01000000 00000000 RW EX4 EI²C EUSB 11100000 00000000 RW PX4 PI²C PUSB 11100000 all bits read-only W = all bits write-only r = read-only bit w = write-only bit b = both read/write bit Page ...

Page 36

... It is recommended to not power I/O with chip power off. Document #: 38-08032 Rev Junction to Case Case to Ambient Temperature Temperature (°C/W) (°C/W) 24.4 23.3 11.9 34.0 15.5 27.7 10.6 14.6 30.9 27 Ca) CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A . Ja Junction to Ambient Temperature . . (°C/W) 47.7 45.9 43.2 25.2 58.6 Page [15] ...

Page 37

... Pin Reset after powered on Notes: 16. Measured at Max VCC, 25°C. 9.1 USB Transceiver USB 2.0-compliant in full- and high-speed modes. 10.0 AC Electrical Characteristics 10.1 USB Transceiver USB 2.0-compliant in full- and high-speed modes. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Conditions 0< V < VCC OUT I = –4 mA OUT Except D+/D– ...

Page 38

... MHz) = 3*t – t – 106 ns ACC1 CL AV DSU t (48 MHz) = 3*t – t – ns. ACC1 CL AV DSU Document #: 38-08032 Rev STBH [18 ACC1 data in Min. Typ. 20.83 41.66 83 9.6 0 CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t AV Max. Unit Notes ns 48 MHz ns 24 MHz ns 12 MHz 10 11 Page ...

Page 39

... ACC2 CL AV DSU t (24 MHz) = 5*t – t –t = 190 ns ACC3 CL AV DSU t (48 MHz) = 5*t – t – ns. ACC3 CL AV DSU Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Stretch = STBH STBL t SCSL t SOEL t [19 DSU ACC1 data in Stretch = 1 [19] t ACC1 Min. Typ. ...

Page 40

... RD# or WR# are active. The address of AUTOPTR2 will be active throughout the cycle and meet the above address valid time for which is based on the stretch value. Document #: 38-08032 Rev STBH data out Stretch = 1 data out Description Min CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A OFF1 t OFF1 Max. Unit Notes 10 ...

Page 41

... READS PORTC RD# Figure 10-5. RD# Strobe Function when PORTC is Accessed by 8051 Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A The way the feature is intended to work is that the RD# signal will prompt the external logic to prepare the next data byte. Nothing gets sampled internally on assertion of the RD# signal itself just a “ ...

Page 42

... Output Propagation Delay XCTL X Notes: 20. Dashed lines denote signals with programmable polarity. 21. GPIF asynchronous RDY signals have a minimum Set-up time when using internal 48-MHz IFCLK. x 22. IFCLK must not exceed 48 MHz. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t IFCLK t SGA t SRY t RYH valid ...

Page 43

... Clock to SLRD Hold Time RDH t SLOE Turn-on to FIFO Data Valid OEon t SLOE Turn-off to FIFO Data Hold OEoff t Clock to FLAGS Output Propagation Delay XFLG t Clock to FIFO Data Output Propagation Delay XFD Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t IFCLK t RDH t SRD t XFLG N N OEon ...

Page 44

... SLRD to FIFO Data Output Propagation Delay XFD t SLOE Turn-on to FIFO Data Valid OEon t SLOE Turn-off to FIFO Data Hold OEoff Note: 23. Slave FIFO asynchronous parameter values use internal IFCLK setting at 48 MHz. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t RDpwh t RDpwl t XFLG t XFD N N+1 ...

Page 45

... SLWR to Clock Set-up Time SWR t Clock to SLWR Hold Time WRH t FIFO Data to Clock Set-up Time SFD t Clock to FIFO Data Hold Time FDH t Clock to FLAGS Output Propagation Time XFLG Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t IFCLK t WRH t SWR SFD FDH t XFLG Description Description ...

Page 46

... PKTEND pin with regards to asserting SLWR. PKTEND can be asserted with the last data value clocked into the FIFOs or thereafter. The only consideration is the set-up time t and the hold time t must be met. SPE PEH Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t WRpwh t WRpwl t t FDH ...

Page 47

... PWpwh t PKTEND to FLAGS Output Propagation Delay XFLG Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A Figure 10-12 shows a scenario where two packets are being committed. The first packet gets committed automatically when the number of bytes in the FIFO reaches X (value set in AUTOINLEN register) and the second one byte/word short packet being committed manually using PKTEND ...

Page 48

... FLAGS DATA Figure 10-15. Slave FIFO Address to Flags/Data Timing Diagram Table 10-16. Slave FIFO Address to Flags/Data Parameters Parameter t FIFOADR[1:0] to FLAGS Output Propagation Delay XFLG t FIFOADR[1:0] to FIFODATA Output Propagation Delay XFD Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t OEoff t OEon Description t XFLG t XFD N N+1 ...

Page 49

... Slave FIFO Asynchronous Address SLCS/FIFOADR [1:0] SLRD/SLWR/PKTEND Figure 10-17. Slave FIFO Asynchronous Address Timing Diagram Slave FIFO Asynchronous Address Parameters Parameter t FIFOADR[1:0] to SLRD/SLWR/PKTEND Set-up Time SFA t RD/WR/PKTEND to FIFOADR[1:0] Hold Time FAH Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t t SFA FAH [21] Description t FAH t SFA [23] ...

Page 50

... During the first read cycle, on the rising edge of the clock the FIFO pointer is updated and increments to point to address N+1. For each subsequent rising edge of IFCLK, while the SLRD is asserted, the FIFO pointer is incre- mented and the next data value is placed on the data bus. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t FAH >= t ...

Page 51

... PKTEND pin at least one clock cycle after the rising edge that caused the last byte/word to be clocked into the previous auto committed packet (the packet with the number of bytes equal to what is set in the AUTOINLEN register). Refer to Figure 10-12 for further details on this timing. CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t FAH >= t ...

Page 52

... RDpwl pulse width SLCS is used then, SLCS must be RDpwh asserted before SLRD is asserted (i.e., the SLCS and SLRD signals must both be asserted to start a valid read condition.) Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t SFA T=0 RDpwl RDpwh ...

Page 53

... If the SLCS is used, it must be in asserted with WRpwh SLWR or before SLWR is asserted. • data must be present on the bus t deasserting edge of SLWR. • deasserting SLWR will cause the data to be written from the data bus to the FIFO and then increments the FIFO Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A t SFA T ...

Page 54

... Ordering Information Table 11-1. Ordering Information Ordering Code Ideal for battery powered applications CY7C68014A-128AXC CY7C68014A-100AXC CY7C68014A-56PVXC CY7C68014A-56LFXC CY7C68014A-56BAXC CY7C68016A-56LFXC Ideal for non-battery powered applications CY7C68013A-128AXC CY7C68013A-128AXI CY7C68013A-100AXC CY7C68013A-100AXI CY7C68013A-56PVXC CY7C68013A-56PVXI CY7C68013A-56LFXC CY7C68013A-56LFXI CY7C68015A-56LFXC CY7C68013A-56BAXC Development Tool Kit CY3684 Reference Design Kit CY4611B Document #: 38-08032 Rev ...

Page 55

... Document #: 38-08032 Rev. *K SIDE VIEW 0.08[0.003] C 1.00[0.039] MAX. 0.05[0.002] MAX. 0.80[0.031] MAX. 0.20[0.008] REF. 0.30[0.012] 0.50[0.020] 0°-12° C SEATING PLANE Figure 12-2. 56-Lead QFN LF56A CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 51-85062-*C BOTTOM VIEW 0.18[0.007] 0.28[0.011] PIN1 ID N 0.20[0.008 0.45[0.018] E-PAD (PAD SIZE VARY BY DEVICE TYPE) ...

Page 56

... MIN. 0.20 MAX. 0. 0.08 MIN. 0°-7° 0.20 MAX. 0.60±0.15 0.20 MIN. 1.00 REF. A DETAIL Figure 12-3. 100-Pin Thin Plastic Quad Flatpack ( 1.4 mm) A100RA Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 81 80 0.30±0.08 0.65 TYP. (8X SEATING PLANE STAND-OFF 0.05 MIN. NOTE: ...

Page 57

... E R 0.08 MIN. 0°-7° 0.20 MAX. 0.60±0.15 0.20 MIN. 1.00 REF. A DETAIL Figure 12-4. 128-Lead Thin Plastic Quad Flatpack ( 1.4 mm) A128 Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 0.22±0.05 12°±1° (8X) 0.50 TYP. SEATING PLANE STAND-OFF NOTE: 0.05 MIN. ...

Page 58

... Note: 24. Source for recommendations: EZ-USB FX2™PCB Design Recommendations, http://www.cypress.com/cfuploads/support/app_notes/FX2_PCB.pdf and High Speed USB Platform Design Guidelines, http://www.usb.org/developers/docs/hs_usb_pdg_r1_0.pdf. Document #: 38-08032 Rev. *K CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A -B- -A- 0.10(4X) REFERENCE JEDEC: MO-195C PACKAGE WEIGHT: 0.02 grams [24] • ...

Page 59

... PCB Material This figure only shows the top three layers of the circuit board: Top Solder, PCB Dielectric, and the Ground Plane Figure 14-3. X-ray Image of the Assembly 2 C system, provided that the system conforms to the I CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A 2 C Standard Specification Page ...

Page 60

... See ECN MON Removed CY7C68013A-56PVXCT part availability Added parts ideal for battery powered applications: CY7C68014A, CY7C68016A Provided additional timing restrictions and requirement regarding the use of PKETEND pin to commit a short one byte/word packet subsequent to committing a packet automatically (when in auto mode). Added Min Vcc Ramp Up time (0 to 3.3v) ...