KSZ8041RNL Micrel Inc, KSZ8041RNL Datasheet - Page 26

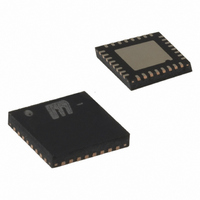

KSZ8041RNL

Manufacturer Part Number

KSZ8041RNL

Description

TXRX 10/100 3.3V PHY RMII 32-MLF

Manufacturer

Micrel Inc

Type

Transceiverr

Specifications of KSZ8041RNL

Number Of Drivers/receivers

1/1

Protocol

RMII

Voltage - Supply

3.135 V ~ 3.465 V

Mounting Type

Surface Mount

Package / Case

32-MLF®, QFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-3503

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

KSZ8041RNL

Manufacturer:

MICREL/麦瑞

Quantity:

20 000

Company:

Part Number:

KSZ8041RNL TR

Manufacturer:

Micrel

Quantity:

1 276

Company:

Part Number:

KSZ8041RNLI TR

Manufacturer:

Micrel

Quantity:

918

Company:

Part Number:

KSZ8041RNLTR

Manufacturer:

NEC

Quantity:

327

Part Number:

KSZ8041RNLTR

Manufacturer:

MICREL/麦瑞

Quantity:

20 000

Company:

Part Number:

KSZ8041RNLU TR

Manufacturer:

Micrel

Quantity:

955

Micrel, Inc.

RMII Signal Definition

The Tables 3 and 4 describe the RMII signals for KSZ8041NL and KSZ8041RNL. Refer to RMII Specification for detailed

information.

Reference Clock (REF_CLK)

REF_CLK is a continuous 50MHz clock that provides the timing reference for TX_EN, TXD[1:0], CRS_DV, RXD[1:0], and

RX_ER.

The KSZ8041NL inputs the 50MHz REF_CLK from the MAC or system board.

The KSZ8041RNL generates the 50MHz RMII REF_CLK and outputs it to the MAC.

Transmit Enable (TX_EN)

TX_EN indicates that the MAC is presenting di-bits on TXD[1:0] for transmission. It is asserted synchronously with the first

nibble of the preamble and remains asserted while all di-bits to be transmitted are presented on the RMII, and is negated

prior to the first REF_CLK following the final di-bit of a frame.

TX_EN transitions synchronously with respect to REF_CLK.

Transmit Data [1:0] (TXD[1:0])

TXD[1:0] transitions synchronously with respect to REF_CLK. When TX_EN is asserted, TXD[1:0] are accepted for

transmission by the PHY. TXD[1:0] is ”00” to indicate idle when TX_EN is de-asserted. Values other than “00” on TXD[1:0]

while TX_EN is de-asserted are ignored by the PHY.

September 2010

RMII

Signal Name

REF_CLK

TX_EN

TXD[1:0]

CRS_DV

RXD[1:0]

RX_ER

RMII

Signal Name

REF_CLK

TX_EN

TXD[1:0]

CRS_DV

RXD[1:0]

RX_ER

Direction

(with respect to PHY,

KSZ8041NL signal)

Input

Input

Input

Output

Output

Output

Direction

(with respect to PHY,

KSZ8041RNL signal)

Output

Input

Input

Output

Output

Output

Table 4. RMII Signal Description – KSZ8041RNL

Table 3. RMII Signal Description – KSZ8041NL

Direction

(with respect to MAC)

Output

Output

Input

Input

Input, or (not required)

Direction

(with respect to MAC)

Input

Output

Output

Input

Input

Input, or (not required)

Input, or Output

26

Description

Synchronous 50 MHz clock reference for

receive, transmit and control interface

Transmit Enable

Transmit Data [1:0]

Carrier Sense/Receive Data Valid

Receive Data [1:0]

Receive Error

Description

Synchronous 50 MHz clock reference for

receive, transmit and control interface

Transmit Enable

Transmit Data [1:0]

Carrier Sense/Receive Data Valid

Receive Data [1:0]

Receive Error

M9999-090910-1.4

KSZ8041NL/RNL