CY7C68000A-56BAXC Cypress Semiconductor Corp, CY7C68000A-56BAXC Datasheet - Page 8

CY7C68000A-56BAXC

Manufacturer Part Number

CY7C68000A-56BAXC

Description

IC USB 2.0 TX2 TXRX 56-VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

CY7Cr

Type

Transceiverr

Datasheet

1.CY7C68000A-56BAXC.pdf

(15 pages)

Specifications of CY7C68000A-56BAXC

Protocol

USB 2.0

Voltage - Supply

3 V ~ 3.6 V

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY3685 - KIT DEV EZ-USB NX2LPCY3683 - KIT EZ-USB TX2 DEVELOPMENT

Number Of Drivers/receivers

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68000A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Table 1. Pin Descriptions (continued)

Document #: 38-08052 Rev. *H

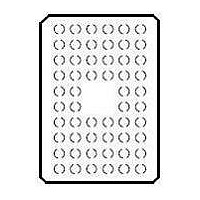

QFN VFBGA

21

22

23

56

51

52

55

17

28

32

45

53

16

20

30

42

47

40

35

25

6

5

A4

B7

A6

A7

A2

H3

H2

A3

C6

C7

D7

E7

E8

C4

C5

C3

D1

D2

G6

C8

F7

F2

RXValid

RXActive

RXError

ValidH

DataBus16_8

XTALIN

XTALOUT

Uni_Bidi

V

V

V

V

V

GND

GND

GND

GND

GND

Reserved

Reserved

Reserved

Reserved

CC

CC

CC

CC

CC

Name

Ground

Ground

Ground

Ground

Ground

Output

Output

Output

Output

INPUT

INPUT

INPUT

INPUT

Power

Power

Power

Power

Power

Type

Input

Input

Input

I/O

Default

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

Receive Data Valid This signal indicates that the DataOut bus has valid

data. The Receive Data Holding Register is full and ready to be unloaded.

The SIE is expected to latch the DataOut bus on the clock edge.

Receive Active This signal indicates that the receive state machine has

detected SYNC and is active.

RXActive is negated after a bit stuff error or an EOP is detected.

Receive Error

0 Indicates no error.

1 Indicates that a receive error has been detected.

ValidH This signal indicates that the high-order eight bits of a 16-bit data

word presented on the Data bus are valid. When DataBus16_8 = 1 and

TXValid = 0, ValidH is an output, indicating that the high-order receive

data byte on the Data bus is valid. When DataBus16_8 = 1 and TXValid

= 1, ValidH is an input and indicates that the high-order transmit data byte,

presented on the Data bus by the transceiver, is valid. When

DataBus16_8 = 0, ValidH is undefined. The status of the receive

low-order data byte is determined by RXValid and are present on D0–D7.

Data Bus 16_8 This signal selects between 8- and 16-bit data transfers.

1–16-bit data path operation enabled. CLK = 30 MHz.

0–8-bit data path operation enabled. When Uni_Bidi = 0, D[8:15] are un-

defined. When Uni_Bidi =1, D[0:7] are valid on TxValid and D[8:15] are

valid on RxValid. CLK = 60 MHz

Note: DataBus16_8 is static after Power-on Reset (POR) and is only

sampled at the end of Reset.

Crystal Input Connect this signal to a 24 MHz parallel-resonant, funda-

mental mode crystal and 30 pF capacitor to GND.

It is also correct to drive XTALIN with an external 24 MHz square wave

derived from another clock source.

Crystal Output Connect this signal to a 24 MHz parallel-resonant, funda-

mental mode crystal and 30 pF (nominal) capacitor to GND. If an external

clock is used to drive XTALIN, leave this pin open.

Driving this pin HIGH enables the unidirectional mode when the 8-bit

interface is selected. Uni_Bidi is static after power-on reset (POR).

V

Ground.

Ground.

Ground.

Ground.

Ground.

Connect pin to Ground.

Connect pin to Ground.

Connect pin to Ground.

Connect pin to Ground.

V

V

V

V

CC

CC

CC

CC

CC

. Connect to 3.3V power source.

. Connect to 3.3V power source.

. Connect to 3.3V power source.

. Connect to 3.3V power source.

. Connect to 3.3V power source.

Description

[1]

(continued)

CY7C68000A

Page 8 of 15

[+] Feedback