CYP15G0401DXB-BGC Cypress Semiconductor Corp, CYP15G0401DXB-BGC Datasheet - Page 21

CYP15G0401DXB-BGC

Manufacturer Part Number

CYP15G0401DXB-BGC

Description

IC TXRX HOTLINK 256LBGA

Manufacturer

Cypress Semiconductor Corp

Series

HOTlink II™r

Type

Transceiverr

Datasheet

1.CYW15G0401DXB-BGXC.pdf

(53 pages)

Specifications of CYP15G0401DXB-BGC

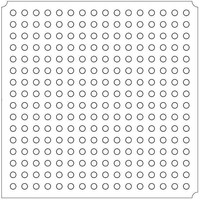

Package / Case

256-LBGA Exposed Pad, 32-HLBGA

Number Of Drivers/receivers

4/4

Protocol

Multiprotocol

Voltage - Supply

3.135 V ~ 3.465 V

Mounting Type

Surface Mount

Product

PHY

Supply Voltage (min)

3.135 V

Supply Current

1.06 A

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Number Of Channels

4

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CYP15G0401DX-EVAL - IC TXRX HOTLINK 256-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CY

Quantity:

767

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CYPRESS

Quantity:

586

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document #: 38-02002 Rev. *L

Serial Output Drivers

The serial interface Output Drivers use high-performance

differential

source-matched drivers for the transmission lines. These

Serial Drivers accept data from the Transmit Shifters. These

outputs have signal swings equivalent to that of standard

PECL drivers, and are capable of driving AC-coupled optical

modules or transmission lines. To acheive OBSAI RP3

compliancy, the serial output drivers must be AC-coupled to

the transmission medium.

When configured for local loopback (LPEN = HIGH), all

enabled Serial Drivers are configured to drive a static differ-

ential logic-1.

Each Serial Driver can be enabled or disabled separately

through the BOE[7:0] inputs, as controlled by the OELE

latch-enable signal. When OELE is HIGH, the signals present

on the BOE[7:0] inputs are passed through the Serial Output

Enable Latch to control the Serial Driver. The BOE[7:0] input

associated with a specific OUTxy± driver is listed in Table 10.

When OELE is HIGH and BOE[x] is HIGH, the associated

Serial Driver is enabled. When OELE is HIGH and BOE[x] is

LOW, the associated Serial Driver is disabled and internally

powered down. If both Serial Drivers for a channel are in this

disabled state, the associated internal logic for that channel is

also powered down. When OELE returns LOW, the values

present on the BOE[7:0] inputs are latched in the Output

Enable Latch, and remain there until OELE returns HIGH to

enable the latch. A device reset (TRSTZ sampled LOW) clears

this latch and disables all Serial Drivers.

Table 10. Output Enable, BIST, and Receive Channel

Enable Signal Map

Transmit PLL Clock Multiplier

The Transmit PLL Clock Multiplier accepts a character-rate or

half-character-rate external clock at the REFCLK input, and

multiples that clock by 10 or 20 (as selected by TXRATE) to

generate a bit-rate clock for use by the Transmit Shifter. It also

provides a character-rate clock used by the transmit paths.

This clock multiplier PLL can accept a REFCLK input between

20 MHz

CYW15G0401DXB), however, this clock range is limited by

the operating mode of the CYP(V)(W)15G0401DXB clock

NOTE: When all transmit channels are disabled (i.e., both

outputs disabled in all channels) and a channel is re-en-

abled, the data on the Serial Drivers may not meet all timing

specifications for up to 200 µs.

BOE[7]

BOE[6]

BOE[5]

BOE[4]

BOE[3]

BOE[2]

BOE[1]

BOE[0]

Input

BOE

and

CML

150 MHz

Controlled

OUTD2±

OUTD1±

OUTC2±

OUTC1±

OUTB2±

OUTB1±

OUTA2±

OUTA1±

(OELE)

Output

(Current

(19.5 MHz

Mode

Transmit D

Transmit C

Transmit B

Transmit A

Receive D

Receive C

Receive B

Receive A

(BISTLE)

Channel

Enable

BIST

Logic)

and

Receive PLL

154 MHz

Receive D

Receive C

Receive B

Receive A

to

Channel

Enable

(RXLE)

X

X

X

X

provide

for

multiplier (controlled by TXRATE) and by the level on the

SPDSEL input.

When TXRATE = HIGH (Half-rate REFCLK), TXCKSEL =

HIGH or MID (TXCLKx or TXCLKA selected to clock input

register) is an invalid mode of operation.

SPDSEL is a static three-level select

selects one of three operating ranges for the serial data

outputs and inputs. The operating serial signaling-rate and

allowable range of REFCLK frequencies are listed in Table 11.

Table 11. Operating Speed Settings

The REFCLK± input is a differential input with each input inter-

nally biased to 1.4V. If the REFCLK+ input is connected to a

TTL, LVTTL, or LVCMOS clock source, REFCLK– can be left

floating and the input signal is recognized when it passes

through the internally biased reference point.

When both the REFCLK+ and REFCLK– inputs are

connected, the clock source must be a differential clock. This

can be either a differential LVPECL clock that is DC- or

AC-coupled, or a differential LVTTL or LVCMOS clock.

By connecting the REFCLK– input to an external voltage

source or resistive voltage divider, it is possible to adjust the

reference point of the REFCLK+ input for alternate logic levels.

When doing so, it is necessary to ensure that the input differ-

ential crossing point remains within the parametric range

supported by the input.

CYP(V)(W)15G0401DXB

Serial Line Receivers

Two differential Line Receivers, INx1± and INx2±, are

available on each channel for accepting serial data streams.

The active Serial Line Receiver on a channel is selected using

the associated INSELx input. The Serial Line Receiver inputs

are differential, and can accommodate wire interconnect and

filtering losses or transmission line attenuation greater than

16 dB. For normal operation, these inputs should receive a

signal of at least VI

differential. Each Line Receiver can be DC- or AC-coupled to

+3.3V powered fiber-optic interface modules (any ECL/PECL

family, not limited to 100K PECL) or AC-coupled to +5V

powered optical modules. The common-mode tolerance of

these line receivers accommodates a wide range of signal

termination voltages. Each receiver provides internal

DC-restoration, to the center of the receiver’s common mode

range, for AC-coupled signals.

The local loopback input (LPEN) allows the serial transmit data

to be routed internally back to the Clock and Data Recovery

circuit associated with each channel. When configured for

MID (Open)

SPDSEL

HIGH

LOW

TXRATE

DIFF

1

0

1

0

1

0

> 100 mV, or 200 mV peak-to-peak

Receive Data Path

CYW15G0401DXB

CYP15G0401DXB

CYV15G0401DXB

Frequency

REFCLK

reserved

19.5–40

80–150

(MHz)

20–40

40–80

40–75

[5]

(ternary) input that

Rate (MBaud)

CYW15G0401

Page 21 of 53

(800-1540 for

Signaling

800–1500

195–400

400–800

DXB)