ISP1582BSUM ST-Ericsson Inc, ISP1582BSUM Datasheet - Page 33

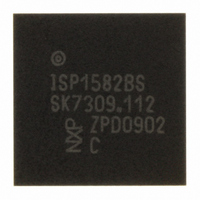

ISP1582BSUM

Manufacturer Part Number

ISP1582BSUM

Description

IC USB PERIPH CONTROLLER 56HVQFN

Manufacturer

ST-Ericsson Inc

Datasheet

1.ISP1582BSUM.pdf

(50 pages)

Specifications of ISP1582BSUM

Applications

USB Host/Peripheral Controller

Interface

USB

Voltage - Supply

3 V ~ 3.6 V

Package / Case

56-VQFN Exposed Pad, 56-HVQFN, 56-SQFN, 56-DHVQFN

Mounting Type

Surface Mount

For Use With

ISP1582 PCI EVALKIT - PCI BUS EVAL KIT ISP1582

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

568-1885-2

ISP1582BS,518

ISP1582BS-T

ISP1582BS,518

ISP1582BS-T

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISP1582BSUM

Manufacturer:

INTEL

Quantity:

828

NXP Semiconductors

AN10039_4

Application note

5.1.3 Handling invalid CBW

5.1.4 Handling error

5.1.5 Handling CBW for an ATA device

A command block is invalid if it has an invalid CBW signature.

If the error_occur flag or transfer_error flag is set, the error must be handled, by stalling

the respective endpoint involved in the transfer.

CBW contains the ATAPI command embedded in the command block.

For an ATA device, the ATAPI packet command must be translated into an ATA

command, before it is issued to the device. The CBWCDB[0] field in CBW contains the

ATAPI command and the remaining field contains command parameters. Based on the

ATAPI command, the corresponding ATA command is selected and issued to the device.

1. Initialize the Endpoint Index register to the respective OUT endpoint.

2. Set the STALL bit in the Control Function register. When the host receives a stall, it

3. Initialize the Endpoint Index register to the respective OUT endpoint, and clear the

4. Set and reset the ENABLE bit in the Endpoint Type register. This will reset the data

5. Initialize the Endpoint Index register to 1 and set the STATUS bit in the Control

6. Wait till the EP0Tx interrupt is received.

7. Wait for the EP0SETUP interrupt, for the bulk-only mass storage reset command.

8. Initialize the Endpoint Index register, by setting the EP0SETUP bit in the Endpoint

9. Read the set-up buffer and re-initialize the ATA or ATAPI device, for a valid mass

• For the data OUT transfer, the respective OUT endpoint is stalled.

• For the data IN transfer, the respective IN endpoint is stalled.

• Clear the error_occur and transfer_error flags.

will send a clear feature command. Wait for the set-up token interrupt for the clear

feature.

STALL bit in the Control Function register.

toggle.

Function register

Index register.

storage reset command.

Rev. 04 — 21 December 2006

ISP1582/83 Firmware Programming Guide

AN10039

© NXP B.V. 2006. All rights reserved.

32 of 49