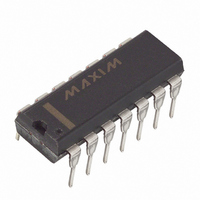

MAX3100EPD+ Maxim Integrated Products, MAX3100EPD+ Datasheet - Page 10

MAX3100EPD+

Manufacturer Part Number

MAX3100EPD+

Description

IC UART SPI MICROWIRE-COMP 14DIP

Manufacturer

Maxim Integrated Products

Type

SPI/MICROWIRE-Compatible UARTr

Datasheet

1.MAX3100CEE.pdf

(24 pages)

Specifications of MAX3100EPD+

Features

Low Power

Number Of Channels

1, UART

Fifo's

8 Byte

Protocol

RS232, RS485

Voltage - Supply

2.7 V ~ 5.5 V

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Cmos

Yes

Mounting Type

Through Hole

Package / Case

14-DIP (0.300", 7.62mm)

Data Rate

115.2 Kbps

Supply Voltage (max)

5.5 V

Supply Voltage (min)

2.7 V

Supply Current

0.27 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Description/function

SPI/MICROWIRE-compatible UART

Mounting Style

Through Hole

Operating Supply Voltage

2.7 V to 5.5 V

No. Of Channels

1

Supply Voltage Range

2.7V To 5.5V

Operating Temperature Range

-40°C To +85°C

Digital Ic Case Style

DIP

No. Of Pins

14

Uart Type

Asynchronous

Supply Voltage Min

2.7V

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Table 5. Bit Descriptions (continued)

SPI/MICROWIRE-Compatible

UART in QSOP-16

Figure 5. Parity and Word-Length Control

10

SHDNo

NAME

SHDNi

RA/FE

BIT

TM

TM

ST

ST

TE

T

______________________________________________________________________________________

WRITE

READ/

w

w

w

w

r

r

r

r

r

TIME

IDLE

IDLE

IDLE

IDLE

STATE

POR

START

START

START

START

0

0

0

0

0

1

0

0

0

PE = 0, L = 0

PE = 0, L = 1

PE = 1, L = 0

PE = 1, L = 1

D0

D0

D0

D0

Receiver-Activity/Framing-Error Bit. In shutdown mode, this is the RA bit. In normal operation,

this is the FE bit. In shutdown mode, a transition on RX sets RA = 1. In normal mode, a fram-

ing error sets FE = 1. A framing error occurs if a zero is received when the first stop bit is

expected. FE is set when a framing error occurs, and cleared upon receipt of the next proper-

ly framed character independent of the FIFO being enabled. When the device wakes up, it is

likely that a framing error will occur. This error can be cleared with a write configuration. The

FE bit is not cleared on a Read Data operation. When an FE is encountered, the UART resets

itself to the state where it is looking for a start bit.

Software-Shutdown Bit. Enter software shutdown with a write configuration where SHDNi = 1.

Software shutdown takes effect after CS goes high, and causes the oscillator to stop as soon

as the transmitter becomes idle. Software shutdown also clears R, T, RA/FE, D0r–D7r,

D0t–D7t, Pr, Pt, and all data in the receive FIFO. RTS and CTS can be read and updated

while in shutdown. Exit software shutdown with a write configuration where SHDNi = 0. The

oscillator restarts typically within 50ms of CS going high. RTS and CTS are unaffected. Refer

to the Pin Description for hardware shutdown (SHDN input).

Shutdown Read-Back Bit. The read-configuration register outputs SHDNo = 1 when the UART

is in shutdown. Note that this bit is not sent until the current byte in the transmitter is sent (T =

1). This tells the processor when it may shut down the RS-232 driver. This bit is also set imme-

diately when the device is shut down through the SHDN pin.

Transmit-Stop Bit. One stop bit will be transmitted when ST = 0. Two stop bits will be transmit-

ted when ST = 1. The receiver only requires one stop bit.

Reads the value of the ST bit.

Transmit-Buffer-Empty Flag. T = 1 means that the transmit buffer is empty and ready to

accept another data word.

Transmit-Enable Bit. If TE = 1, then only the RTS pin will be updated on CS’s rising edge. The

contents of RTS, Pt, and D0t–D7t transmit on CS’s rising edge when TE = 0.

Mask for T bit. IRQ is asserted if TM = 1 and T = 1 (Table 6).

Reads the value of the TM bit (Table 6).

D1

D1

D1

D1

D2

D2

D2

D2

D3

D3

D3

D3

D4

D4

D4

D4

D5

D5

D5

D5

D6

D6

D6

D6

DESCRIPTION

STOP

SECOND STOP BIT IS OMITTED IF ST = 0.

D7

D7

Pt

STOP

STOP

STOP

Pt

STOP

STOP

STOP

IDLE

STOP

IDLE

IDLE

IDLE