N80C452 Intel Corporation, N80C452 Datasheet

N80C452

Available stocks

Related parts for N80C452

N80C452 Summary of contents

Page 1

... Intel products except as provided in Intel’s Terms and Conditions of Sale for such products Intel retains the right to make changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata COPYRIGHT INTEL CORPORATION 1996 UPI-452 8 Mask Programmable Internal ROM ...

Page 2

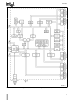

UPI-452 Figure 1 Architectural Block Diagram 2 231428 – 1 ...

Page 3

Figure 1 Architectural Block Diagram (Continued) UPI-452 231428 – ...

Page 4

UPI-452 TABLE OF CONTENTS CONTENTS Introduction Table of Contents List of Tables and Figures Pin Description Architectural Overview Introduction FIFO Buffer Interface FIFO Programmable Features Immediate Commands DMA FIFO Slave Interface Functional Description Overview Input FIFO Channel Output FIFO Channel ...

Page 5

LIST OF TABLES AND FIGURES Figures 1 Architectural Block Diagram 2 UPI 452 68-Pin PLCC Pinout Diagram 3 UPI-452 Conceptual Block Diagram 4 UPI-452 Functional Block Diagram 5 Input FIFO Channel Functional Block Diagram 6 Output FIFO Channel Functional Block ...

Page 6

UPI-452 P C Board View As Viewed from the Component Side of the P C Board Figure 2 UPI 452 68-Pin PLCC Pinout Diagram 6 (Underside of Socket) 231428 –32 ...

Page 7

UPI MICROCONTROLLER FAMILY The UPI-452 joins the current members of the UPI microcontroller family UPI’s are derivatives of the MCS TM family of microcontrollers Because of their on-chip system bus interface UPI’s are designed to be system bus ‘‘slaves’’ while ...

Page 8

UPI-452 UPI-452 PIN DESCRIPTIONS Symbol Pin Type Port (A0–A7) (HLD HLDA Port (A8–A15 ...

Page 9

UPI-452 PIN DESCRIPTIONS Symbol Pin Type Port RST 20 I ALE 18 O PSEN DB0 58 ...

Page 10

UPI-452 UPI-452 PIN DESCRIPTIONS Symbol Pin Type INTRQ 50 O DACK ARCHITECTURAL OVERVIEW Introduction The UPI-452 slave microcontroller incorporates an 80C51 with double the program and data memory a slave interface which allows it ...

Page 11

Figure 4 UPI-452 Functional Block Diagram The division of the 128 bytes between Input and Output channels is user programmable allowing maximum flexibility If the entire 128 byte FIFO is allocated to the Input channel a high performance Host can ...

Page 12

UPI-452 FIFO Read Write Pointers These normally operate in auto-increment (and auto- rollover) mode but can be reassigned by the internal CPU during FIFO DMA Freeze Mode (See FIFO-Ex- ternal Host Interface FIFO DMA Freeze Mode de- scription) Threshold Register ...

Page 13

Input FIFO Channel The Input FIFO Channel provides for data transfer from the external Host to the internal CPU (Figure 5) The registers associated with the Input Channel during normal operation are listed in Table 1 Table 1 Input FIFO ...

Page 14

UPI-452 The host CPU writes data and Data Stream Com- mands into the Input Buffer Latch on the rising edge of the external WR signal External addressing de- termines whether the byte is a data byte or Data Stream Command ...

Page 15

Figure 6 Output FIFO Channel Functional Block Diagram Table 2 Output FIFO Channel Registers Register Name 1) Output Buffer Latch 2) FIFO OUT SFR 3) COMMAND OUT SFR 4) Output FIFO Read Pointer SFR 5) Output FIFO Write Pointer SFR ...

Page 16

UPI-452 The UPI-452 internal CPU transfers data to the Out- put FIFO via the FIFO OUT SFR and commands via the COMMAND OUT SFR If the byte is written to the COMMAND OUT SFR the ninth bit is automati- cally ...

Page 17

Figure 7a Handshake Mechanisms for Handling Immediate Command IN Flowchart 231428– 11 Figure 7b Handshake Mechanisms for Handling Immediate Command OUT Flowchart UPI-452 231428 –12 17 ...

Page 18

UPI-452 HOST SLAVE INTERFACE SPECIAL FUNCTION REGISTERS Slave Interface Special Function Registers The Internal CPU interfaces with the FIFO slave module via the following registers 1) Mode Special Function Register (MODE) 2) Slave Control Special Function Register (SLCON) 3) Slave ...

Page 19

... A ‘1’ will be read from all SFR reserved locations except HCON SFR HC0 and HC2 ‘reserved’ these locations are reserved for future use by Intel Corporation 3) Slave Status SFR (SSTAT) The bits in the Slave Status SFR reflect the status of the FIFO-internal CPU interface It can be read during an ...

Page 20

UPI-452 SST7 Output FIFO Overrun Error Condition 1 No Error e 0 Error (latched until Slave Status SFR is read) e SST6 Immediate Command Out Register Status 1 Full (i e Host CPU has not read previous Immediate Command Out ...

Page 21

... A ‘1’ will be read from all SFR reserved locations except HCON SFR HC0 and HC2 ‘reserved’ these locations are reserved for future use by Intel Corporation 2) Host Status SFR (HSTAT) The Host Status SFR provides information on the FIFO-Host Interface and can be used to determine the ...

Page 22

UPI-452 HST7 Output FIFO Underrun Error Condition 1 No Underrun Error e 0 Underrun Error (latched until Host e Status Register is read) HST6 Immediate Command Out SFR Status 1 Empty e 0 Immediate Command Present e HST5 Data Stream ...

Page 23

Table 3 UPI-452 Address Decoding DACK Operation Data or DMA from Output FIFO Channel Data Stream Command from Output FIFO ...

Page 24

UPI-452 DMA Requests to the Host The UPI-452 generates two DMA requests DRQIN and DRQOUT to facilitate data transfer between the Host and the Input and Output FIFO channels A DMA acknowledge DACK is used as a chip select and ...

Page 25

The FIFO IN COMMAND IN and Immediate Com- mand In SFRs are read only registers Any write op- eration performed on these registers will be ignored and the FIFO pointers will remain intact The internal CPU uses the FIFO OUT ...

Page 26

UPI-452 Table 4 DMA Accessible Special Function Registers SFR Symbol Accumulator A ACC B Register B FIFO IN FIN COMMAND IN CIN FIFO OUT FOUT COMMAND OUT COUT Serial Data Buffer SBUF Port 0 P0 Port 1 P1 Port 2 ...

Page 27

DONE DMA transfer Flag 0 DMA transfer is not completed 1 DMA transfer is complete NOTE This flag is set when contents of the Byte Count SFR decrements to zero It is reset automatically when the DMA vectors to its ...

Page 28

UPI-452 NOTE All interrupts including FIFO interrupts are not rec- ognized in Burst Mode Burst Mode transfers should be used to service the FIFO only when the user is certain that no Data Stream Commands are in the block to ...

Page 29

EXTERNAL DEMAND MODE The DMA can be initiated by an external device via External interrupt 0 and 1 (INT0 INT1) pins The INT0 pin demands DMA0 (Channel 0) and INT1 de- mands DMA1 (Channel 1) If the interrupts are ...

Page 30

UPI-452 When a DMA operation is complete (BCR decre- ments to zero) the DONE flag in the respective DCON (DCON0 or DCON1) SFR is set If the DMA interrupt is enabled the DONE flag is reset automat- ically upon vectoring ...

Page 31

Figure 8 DMA Transfer from External Memory to External Memory Figure 9 DMA Transfer from External Memory to Internal Memory Figure 10 DMA Transfer from Internal Memory to External Memory UPI-452 231428 –13 231428 –14 231428 –15 31 ...

Page 32

UPI-452 Figure 11 DMA Transfer from Internal Memory to Internal Memory INTERNAL INTERRUPTS Overview The UPI-452 provides a total of eight interrupt sourc- es (Table 6) Their operation is the same as in the 80C51 with the addition of three ...

Page 33

A Data Stream Command Interrupt is generated whenever there is a Data Stream Command in the COMMAND IN SFR The interrupt is generated to ensure that the internal interrupt is recognized be- fore another instruction is executed Immediate Command Interrupts ...

Page 34

UPI-452 Interrupt Priority SFR (IP) A priority level may be assigned to each interrupt source with 1 being higher priority level through the IP and the IEP (Interrupt Enable and Priority) SFR A priority level of ...

Page 35

FIFO-EXTERNAL HOST INTERFACE FIFO DMA FREEZE MODE Overview During FIFO DMA Freeze Mode the internal CPU can reconfigure the FIFO interface FIFO DMA Freeze Mode is provided to prevent the Host from accessing the FIFO during a reconfiguration se- quence ...

Page 36

UPI-452 The UPI-452 can also be programmed to interrupt the Host following power on reset in order to indi- cate to the Host that FIFO DMA Freeze Mode is in progress This is done by enabling the INTRQ inter- rupt ...

Page 37

External Host writing to the Immediate Command In SFR and the Host Control SFR is also inhibited when the slave bus interface is frozen Writing to these two registers after FIFO DMA Freeze Mode is invoked will also cause HST3 ...

Page 38

UPI-452 Table 9 FIFO SFR’s Characteristics During FIFO DMA Freeze Mode Label Name HCON Host Control HSTAT Host Status SLCON Slave Control SSTAT Slave Status IEP Interrupt Enable MODE Mode Register IWPR Input FIFO Write Pointer IRPR Input FIFO Read ...

Page 39

Input and Output FIFO Threshold SFR (ITHR OTHR) The Input and Output FIFO Threshold SFRs are also programmable by the internal CPU during FIFO DMA Freeze Mode For proper operation of the Threshold feature the Threshold SFR should be changed ...

Page 40

UPI-452 HST5 Data Stream Command at Output FIFO This bit is forced to a ‘‘1’’ during FIFO DMA Freeze Mode to prevent the external host CPU from trying to read the DSC Once nor- mal operation is resumed HST5 will ...

Page 41

SST1 Data Stream Command at Input FIFO Flag In FIFO DMA Freeze Mode this bit operates normally It indicates whether the next byte of data from the Input FIFO is a DSC or data byte DSC ...

Page 42

UPI-452 Table 11b 80C51 Special Function Registers Symbol Name Address Contents ACC Accumulator 0E0H B B Register 0F0H PSW Program Status 0D0H Word SP Stack Pointer 81H DPTR Data Pointer 82H (consisting of DPH and DPL) P0 Port 0 80H ...

Page 43

Miscellaneous Special Function Register Description 80C51 SFRs ACCUMULATOR ACC is the Accumuator SFR The mnemonics for accumulator-specific instructions however refer to the accumulator simply REGISTER The B SFR is used during multiply and divide opera- tions For ...

Page 44

UPI-452 Symbolic Address PSW CY AC (MSB) Symbol Position CY PSW 7 AC PSW 6 F0 PSW 5 RS1 PSW 4 RS0 PSW 3 OV PSW 2 PSW 1 P PSW 0 (RS1 RS0) enable internal RAM register banks as ...

Page 45

ABSOLUTE MAXIMUM RATINGS Ambient Temperature Under Bias Storage Temperature Voltage on Any Pin Voltage Power Dissipation D C ...

Page 46

UPI-452 D C CHARACTERISTICS Symbol Parameter I Input Leakage Current LI (except Ports Output Leakage Current OZ (except Ports Operating Current CC I Idle Mode Current CCI ...

Page 47

A C CHARACTERISTICS Port 0 ALE and PSEN 100 pF Load Capacitance for All Other Outputs e EXTERNAL PROGRAM AND DATA MEMORY CHARACTERISTICS Symbol Parameter 1 TCLCL Oscillator Frequency TLHLL ALE Pulse Width TAVLL Address Valid to ...

Page 48

UPI-452 EXTERNAL DATA MEMORY READ CYCLE EXTERNAL PROGRAM MEMORY READ CYCLE 48 231428 –19 231428 –20 ...

Page 49

EXTERNAL DATA MEMORY WRITE CYCLE SHIFT REGISTER MODE TIMING WAVEFORMS UPI-452 231428 –21 231428 –22 49 ...

Page 50

UPI-452 EXTERNAL CLOCK DRIVE Symbol Parameter 1 TCLCL Oscillator Frequency TCHCX High Time TCLCX Low Time TCLCH Rise Time TCHCL Fall Time NOTE External clock timings are sampled not tested on all parts SERIAL PORT TIMING SHIFT REGISTER MODE Test ...

Page 51

HLD HLDA WAVEFORMS Arbiter Mode Requestor Mode HLD HLDA TIMINGS Test Conditions Symbol Parameter THMIN HLD Pulse Width THLAL HLD to HLDA Delay if HLDA is Granted THHAH HLD to ...

Page 52

UPI-452 HOST PORT WAVEFORMS HOST PORT TIMINGS Test Conditions Symbol Parameter TCC Cycle Time TPW Command Pulse Width TRV Recovery Time TAS Address Setup Time TAH Address Hold Time TDS WRITE ...

Page 53

REVISION HISTORY DOCUMENT UPI-452 Data Sheet OLD REVISION NUMBER 231428-005 NEW REVISION NUMBER 231428-006 1 Maximum Clock Rate was changed from 16 MHz to 14 MHz This change is reflected in all Maximum Timing specifications 2 The proper range of ...