MC14518B, MC14520B

Dual Up Counters

counter are constructed with MOS P−channel and N−channel

enhancement mode devices in a single monolithic structure. Each

consists of two identical, independent, internally synchronous 4−stage

counters. The counter stages are type D flip−flops, with interchangeable

Clock and Enable lines for incrementing on either the positive−going or

negative−going transition as required when cascading multiple stages.

Each counter can be cleared by applying a high level on the Reset line.

In addition, the MC14518B will count out of all undefined states within

two clock periods. These complementary MOS up counters find

primary use in multi−stage synchronous or ripple counting applications

requiring low power dissipation and/or high noise immunity.

Features

•

•

•

•

•

•

Maximum ratings are those values beyond which device damage can occur.

Maximum ratings applied to the device are individual stress limit values (not

normal operating conditions) and are not valid simultaneously. If these limits are

exceeded, device functional operation is not implied, damage may occur and

reliability may be affected.

1. Maximum Ratings are those values beyond which damage to the device

2. Temperature Derating:

static voltages or electric fields. However, precautions must be taken to avoid

applications of any voltage higher than maximum rated voltages to this

high−impedance circuit. For proper operation, V

to the range V

either V

MAXIMUM RATINGS

© Semiconductor Components Industries, LLC, 2006

Symbol

V

The MC14518B dual BCD counter and the MC14520B dual binary

I

This device contains protection circuitry to guard against damage due to high

Unused inputs must always be tied to an appropriate logic voltage level (e.g.,

of Clock or Negative Transition on Enable

Schottky TTL Load Over the Rated Temperature Range

Diode Protection on All Inputs

Supply Voltage Range = 3.0 Vdc to 18 Vdc

Internally Synchronous for High Internal and External Speeds

Logic Edge−Clocked Design — Incremented on Positive Transition

Capable of Driving Two Low−power TTL Loads or One Low−power

Pb−Free Packages are Available*

in

in

may occur.

Plastic “P and D/DW” Packages: – 7.0 mW/_C From 65_C To 125_C

V

T

P

, I

T

T

, V

stg

DD

A

D

L

out

out

SS

or V

DC Supply Voltage Range

Input or Output Voltage Range

Input or Output Current

Power Dissipation,

Operating Temperature Range

Storage Temperature Range

Lead Temperature

SS

DD

(DC or Transient)

(DC or Transient) per Pin

per Package (Note 2.)

(8−Second Soldering)

v (V

). Unused outputs must be left open.

in

Parameter

or V

(Voltages Referenced to V

out

) v V

DD

.

in

and V

−0.5 to V

−0.5 to +18.0

SS

−55 to +125

−65 to +150

out

) (Note 1.)

Value

±10

500

260

should be constrained

DD

+ 0.5

1

Unit

mW

mA

°C

°C

°C

V

V

See detailed ordering and shipping information in the package

dimensions section on page 7 of this data sheet.

ORDERING INFORMATION

xx

A

WL, L

YY, Y

WW, W

G

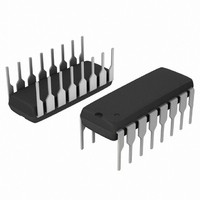

DW SUFFIX

CASE 751G

SOEIAJ−16

CASE 966

CASE 648

F SUFFIX

P SUFFIX

SOIC−16

PDIP−16

= 18 or 20

= Assembly Location

= Wafer Lot

= Year

= Work Week

= Pb−Free Indicator

Publication Order Number:

16

16

1

16

1

1

DIAGRAMS

MC145xxBCP

AWLYYWWG

AWLYYWWG

MARKING

MC145xxB

MC14518B/D

ALYWG

145xxB