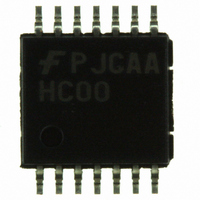

MM74HC00MTCX Fairchild Semiconductor, MM74HC00MTCX Datasheet

MM74HC00MTCX

Specifications of MM74HC00MTCX

MM74HC00MTCXTR

Available stocks

Related parts for MM74HC00MTCX

MM74HC00MTCX Summary of contents

Page 1

... All packages are lead free per JEDEC: J-STD-020B standard. Connection Diagram Pin Assignments for DIP, SOIC, SOP and TSSOP Top View ©1983 Fairchild Semiconductor Corporation MM74HC00 Rev. 1.3.0 General Description The MM74HC00 NAND gates utilize advanced silicon- gate CMOS technology to achieve operating speeds similar to LS-TTL gates with the low power consumption of standard CMOS integrated circuits ...

Page 2

... V DC Input or Output Voltage IN OUT T Operating Temperature Range Input Rise or Fall Times 2. 4. 6.0V CC ©1983 Fairchild Semiconductor Corporation MM74HC00 Rev. 1.3.0 (1) Parameter Parameter 2 Rating –0.5 to +7.0V –1 +1.5V CC –0 +0.5V CC ±20mA ±25mA ±50mA –65°C to +150°C 600mW 500mW 260°C Min ...

Page 3

... For a power supply of 5V ±10% the worst case output voltages (V values should be used when designing with this supply. Worst case V respectively. (The V value at 5.5V is 3.85V.) The worst case leakage current (I IH the higher voltage and so the 6.0V values should be used. ©1983 Fairchild Semiconductor Corporation MM74HC00 Rev. 1.3.0 ( ...

Page 4

... Maximum Output TLH THL Rise and Fall Time C Power Dissipation PD (4) Capacitance C Maximum Input IN Capacitance Note determines the no load dynamic power consumption current consumption ©1983 Fairchild Semiconductor Corporation MM74HC00 Rev. 1.3 6ns r f Conditions = t = 6ns (unless otherwise specified (V) Conditions Typ. CC 2 ...

Page 5

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 6

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 7

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 8

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 9

... TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended exhaustive list of all such trademarks. ® ACEx Build it Now™ CorePLUS™ CROSSVOLT™ CTL™ Current Transfer Logic™ ...