DS1248WP-120+ Maxim Integrated Products, DS1248WP-120+ Datasheet - Page 4

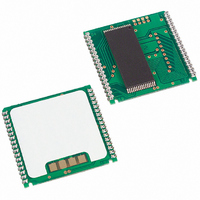

DS1248WP-120+

Manufacturer Part Number

DS1248WP-120+

Description

IC NVSRAM 1MBIT 120NS 34PCM

Manufacturer

Maxim Integrated Products

Datasheet

1.DS1248W-120.pdf

(18 pages)

Specifications of DS1248WP-120+

Format - Memory

RAM

Memory Type

NVSRAM (Non-Volatile SRAM)

Memory Size

1M (128K x 8)

Speed

120ns

Interface

Parallel

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Package / Case

34-PowerCap™ Module

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

RAM READ MODE

The DS1248 executes a read cycle whenever WE (write enable) is inactive (high) and CE (chip enable) is

active (low). The unique address specified by the 17 address inputs (A0–A16) defines which of the 128k

bytes of data is to be accessed. Valid data will be available to the eight data-output drivers within t

(access time) after the last address input signal is stable, providing that CE and OE (output enable) access

times and states are also satisfied. If OE and CE access times are not satisfied, then data access must be

measured from the later occurring signal (CE or OE) and the limiting parameter is either t

for OE, rather than address access.

RAM WRITE MODE

The DS1248 is in the write mode whenever the WE and CE signals are in the active (low) state after

address inputs are stable. The latter occurring falling edge of CE or WE will determine the start of the

write cycle. The write cycle is terminated by the earlier rising edge of CEor WE. All address inputs must

be kept valid throughout the write cycle. WE must return to the high state for a minimum recovery time

(t

write cycles to avoid bus contention. However, if the output bus has been enabled (CE and OE active)

then WE will disable the outputs in t

DATA RETENTION MODE

The 5V device is fully accessible and data can be written or read only when V

However, when V

internal clock registers and SRAM are blocked from any access. When V

point, V

operation and SRAM data are maintained from the battery until V

The 3.3V device is fully accessible and data can be written or read only when V

When V

switched from V

the device power is switched from V

operation and SRAM data are maintained from the battery until V

All control, data, and address signals must be powered down when V

WR

) before another cycle can be initiated. The OE control signal should be kept inactive (high) during

SO

CC

(battery supply level), device power is switched from the V

falls below V

CC

CC

to the backup supply (V

is below the power-fail point, V

PF

, access to the device is inhibited. If V

ODW

CC

to the backup supply (V

from its falling edge.

BAT

) when V

4 of 18

PF

CC

(point at which write protection occurs), the

drops below V

BAT

PF

CC

CC

is less than V

is returned to nominal levels.

is returned to nominal levels.

) when V

CC

CC

is powered-down.

CC

pin to the backup battery. RTC

PF

falls below the battery switch

. If V

CC

drops below V

BAT

PF

CC

CC

, the device power is

is greater than V

is greater than V

is greater than V

CO

for CE or t

BAT

. RTC

BAT

ACC

PF

OE

PF

.

,

.