LNBH23PPR STMicroelectronics, LNBH23PPR Datasheet - Page 16

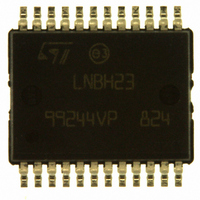

LNBH23PPR

Manufacturer Part Number

LNBH23PPR

Description

IC LNB SUPPLY/CTRL POWERSSO-24

Manufacturer

STMicroelectronics

Datasheet

1.LNBH23PPR.pdf

(32 pages)

Specifications of LNBH23PPR

Applications

Converter, Analog and Digital STB Receivers/SatTV

Voltage - Input

8 ~ 15 V

Number Of Outputs

1

Voltage - Output

13.4V, 18.5V

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

PowerSSO-24

Output Voltage

25 V

Output Current

1000 mA

Input Voltage

8 V to 15 V

Switching Frequency

220 KHz

Operating Temperature Range

- 25 C to + 125 C

Mounting Style

Through Hole

Duty Cycle (max)

57 %

For Use With

497-8717 - DEMO BOARD BASED ON LNBH23497-8336 - BOARD EVAL BASED ON LNBH23

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-6121-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

LNBH23PPR

Manufacturer:

ST

Quantity:

20 000

Part Number:

LNBH23PPR-MYS

Manufacturer:

ST

Quantity:

20 000

Part Number:

LNBH23PPR/1B

Manufacturer:

ST

Quantity:

20 000

LNBH23 software description

7

7.1

7.2

7.3

16/32

S

Mode

Write

Read

0

MSB

0

LNBH23 software description

Interface protocol

The interface protocol comprises:

●

●

●

●

ACK = Acknowledge

S = Start

P = Stop

R/W = 1/0, Read/Write bit

X = 0/1, two selectable addresses available through ADDR pin (see Address pin

characteristics

System register (SR, 1 byte)

Write = control bits functions in write mode

Read= diagnostic bits in read mode.

All bits reset to 0 at power On

Transmitted data (I²C bus write mode)

When the R/W bit in the chip address is set to 0, the main MCU can write on the system

register (SR) of the LNBH23 via I²C bus. All and 8 bits are available and can be written by

the MCU to control the device functions as per the below truth table.

IMON

MSB

PCL

0

A start condition (S)

A chip address byte (the LSB bit determines read(=1)/write(=0) transmission)

A sequence of data (1 byte + acknowledge)

A stop condition (P)

Chip address

1

VMON

TTX

0

Table

1

10)

TMON

X

TEN

R/W ACK

LSB

Doc ID 13356 Rev 7

LLC

LLC

MSB

VSEL

VSEL

Data

EN

EN

ITEST

OTF

LSB

ACK

LNBH23

LSB

AUX

OLF

P