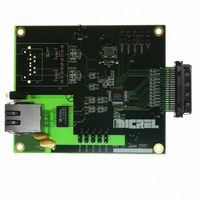

KSZ8041TL-EVAL Micrel Inc, KSZ8041TL-EVAL Datasheet

KSZ8041TL-EVAL

Specifications of KSZ8041TL-EVAL

KSZ8041TL-EVAL

Related parts for KSZ8041TL-EVAL

KSZ8041TL-EVAL Summary of contents

Page 1

... KSZ8041TL/FTL 10Base-T/100Base-TX/100Base-FX Physical Layer Transceiver Data Sheet Rev. 1.1 The KSZ8041TL represents a new level of features and performance and is an ideal choice of physical layer transceiver for 10Base-T/100Base-TX applications. The KSZ8041FTL has all the identical rich features of the KSZ8041TL plus 100Base-FX support for fiber and media converter applications ...

Page 2

... TDR-based cable diagnostics for identification of faulty copper cabling • Fiber support: 100Base-FX (KSZ8041FTL only), Back- to-Back mode (KSZ8041FTL and KSZ8041TL) • MII interface support • RMII interface support with external 50MHz system clock • SMII interface support with external 125MHz system clock and 12.5MHz sync clock from MAC • ...

Page 3

... Changed polarity (swapped definition) of DUPLEX strapping pin. Removed DUPLEX strapping pin update to Register 4h – Auto-Negotiation Advertisement bits [8, 6]. Added Back-to-Back mode for KSZ8041TL. Added Symbol Error to MII/RMII Receive Error description and Register 15h – RXER Counter. Added a 100pF capacitor on REXT (pin 16) in Pin Description table. ...

Page 4

... Serial MII (SMII) Data Interface ........................................................................................................................................ 24 SMII Signal Definition ....................................................................................................................................................... 24 Clock Reference (CLOCK) ......................................................................................................................................... 24 Sync Pulse (SYNC) ..................................................................................................................................................... 24 Transmit Data and Control (TX) ................................................................................................................................ 24 Receive Data and Control (RX).................................................................................................................................. 25 Collision Detection ..................................................................................................................................................... 26 HP Auto MDI/MDI-X.......................................................................................................................................................... 27 Straight Cable ............................................................................................................................................................. 27 Crossover Cable ......................................................................................................................................................... 28 ® LinkMD Cable Diagnostics.............................................................................................................................................. 29 Access ......................................................................................................................................................................... 29 Usage ........................................................................................................................................................................... 29 April 2007 4 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 5

... MII SQE Timing (10Base-T) ............................................................................................................................................. 45 MII Transmit Timing (10Base-T) ....................................................................................................................................... 46 MII Receive Timing (10Base-T) ........................................................................................................................................ 47 MII Transmit Timing (100Base-TX) .................................................................................................................................. 48 MII Receive Timing (100Base-TX) ................................................................................................................................... 49 RMII Timing....................................................................................................................................................................... 50 Auto-Negotiation Timing ................................................................................................................................................... 51 MDC/MDIO Timing ........................................................................................................................................................... 52 Reset Timing..................................................................................................................................................................... 53 Reset Circuit ........................................................................................................................................................................ 54 Selection of Isolation Transformer.................................................................................................................................... 56 Selection of Reference Crystal .......................................................................................................................................... 56 Package Information........................................................................................................................................................... 57 April 2007 5 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 6

... Figure 7. 50MHz Oscillator Reference Clock for RMII Mode............................................................................................... 30 Figure 8. 125MHz Oscillator Reference Clock for SMII Mode ............................................................................................. 30 Figure 9. KSZ8041TL/FTL Power and Ground Connections............................................................................................... 31 Figure 10. KSZ8041FTL / KSZ8041TL Back-to-Back Media Converter .............................................................................. 33 Figure 11. MII SQE Timing (10Base-T) ............................................................................................................................... 45 Figure 12. MII Transmit Timing (10Base-T) ......................................................................................................................... 46 Figure 13. MII Receive Timing (10Base-T) .......................................................................................................................... 47 Figure 14 ...

Page 7

... Table 6. SMII TXD[0:7] Encoding Table .............................................................................................................................. 25 Table 7. SMII RX Bit Description.......................................................................................................................................... 26 Table 8. SMII RXD[0:7] Encoding Table .............................................................................................................................. 26 Table 9. MDI/MDI-X Pin Definition ....................................................................................................................................... 27 Table 10. KSZ8041TL/FTL Power Pin Description .............................................................................................................. 31 Table 11. Copper and Fiber Mode Selection ....................................................................................................................... 32 Table 12. MII Signal Connection for MII Back-to-Back Mode .............................................................................................. 33 Table 13. RMII Signal Connection for RMII Back-to-Back Mode......................................................................................... 34 Table 14 ...

Page 8

... Pin Configuration GND 2 GND 3 GND 4 VDDA_1.8 5 VDDA_1.8 6 V1.8_OUT 7 VDDA_3.3 8 VDDA_3.3 9 RX- 10 RX+ 11 TX April 2007 KSZ8041TL 48-Pin TQFP 8 KSZ8041TL/FTL TXD1 / TXD[1] / SYNC TXD0 / TXD[ TXEN / TX_EN TXC INTRP VDD_1.8 GND RXER / RX_ER / ISO RXC RXDV / CRSDV / CONFIG2 VDDIO_3.3 VDDIO_3 M9999-042707-1 ...

Page 9

... Micrel, Inc GND 2 GND 3 GND 4 VDDA_1.8 5 VDDA_1.8 6 V1.8_OUT 7 VDDA_3.3 8 VDDA_3.3 9 RX- 10 RX+ 11 TX April 2007 KSZ8041FTL 48-Pin TQFP 9 KSZ8041TL/FTL TXD1 / TXD[1] / SYNC TXD0 / TXD[ TXEN / TX_EN TXC INTRP VDD_1.8 GND RXER / RX_ER / ISO RXC RXDV / CRSDV / CONFIG2 VDDIO_3.3 VDDIO_3 M9999-042707-1 ...

Page 10

... SMII Mode: 125MHz +/-100ppm (oscillator, or external clock only) I/O Set physical transmit output current Connect a 6.49KΩ resistor in parallel with a 100pF capacitor to ground on this pin. See KSZ8041TL-FTL reference schematics. Gnd Ground I/O Management Interface (MII) Data I/O This pin requires an external 4.7KΩ pull-up resistor. ...

Page 11

... See “Strapping Options” section for details. Ipd/O MII Mode: Carrier Sense Output / Config Mode: The pull-up/pull-down value is latched as CONFIG1 during power-up / reset. See “Strapping Options” section for details. 11 (2) / (3) / (4) / Transmit Clock Output Transmit Clock Input (5) / (6) / (7) (5) / (6) / (5) / (5) / KSZ8041TL/FTL M9999-042707-1.1 ...

Page 12

... The LED0 pin is programmable via register 1Eh bits [15:14], and is defined as follows. LED mode = [00] Link/Activity Pin State No Link H Link L Activity Toggle LED mode = [01] Link Pin State No Link H Link L LED mode = [10] Reserved LED mode = [11] Reserved 12 KSZ8041TL/FTL LED Definition OFF ON Blinking LED Definition OFF ON LED Definition OFF ON Blinking LED Definition OFF ON M9999-042707-1.1 ...

Page 13

... LED mode = [00] Speed Pin State 10BT H 100BT L LED mode = [01] Activity Pin State No Activity H Activity Toggle LED mode = [10] Reserved LED mode = [11] Reserved - No connect - No connect - No connect 13 KSZ8041TL/FTL LED Definition OFF ON LED Definition OFF Blinking LED Definition OFF ON LED Definition OFF Blinking M9999-042707-1.1 ...

Page 14

... Chip Reset (active low connect Ipd FXSD: Signal Detect for 100Base-FX fiber mode FXEN: Fiber Enable for 100Base-FX fiber mode If FXEN=0, fiber mode is disabled. PHY is in copper mode. The default is “0”. See “100Base-FX Operation” section for details. 14 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 15

... During power-up / reset, this pin value is latched into register 0h bit 13 as the Speed Select, and also is latched into register 4h (Auto-Negotiation Advertisement) as the Speed capability support. If fiber mode (FXEN=1), pin strap- FEF. Pull-up (default) = Enable Far-End Fault Pull-down = Disable Far-End Fault This pin value is latched during power-up / reset. 15 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 16

... During power-up / reset, this pin value is latched into register 0h bit 12. Ipu/O If copper mode (FXEN=0), pin strap-in is Nway Auto-Negotiation Enable. Pull-up (default) = Enable Auto-Negotiation Pull-down = Disable Auto-Negotiation During power-up / reset, this pin value is latched into register 0h bit 12. If fiber mode (FXEN=1), this pin configuration is always strapped to disable Auto- Negotiation. 16 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 17

... On the media side, the KSZ8041TL supports 10Base-T and 100Base-TX with HP auto MDI/MDI-X for reliable detection of and correction for straight-through and crossover cables. The KSZ8041TL offers a choice of MII, RMII, or SMII data interface connection to a MAC processor. The MII management bus option gives the MAC processor complete access to the KSZ8041TL control and status registers. Additionally, an interrupt pin eliminates the need for the processor to poll for PHY status change ...

Page 18

... Priority 4: 10Base-T, half-duplex If auto-negotiation is not supported or the KSZ8041TL/FTL link partner is forced to bypass auto-negotiation, the KSZ8041TL/FTL sets its operating mode by observing the signal at its receiver. This is known as parallel detection, and allows the KSZ8041TL/FTL to establish link by listening for a fixed signal protocol in the absence of auto-negotiation advertisement protocol ...

Page 19

... Force Link Setting Yes Bypass Auto Negotiation and Set Link Mode April 2007 N Parallel Operation o Attempt Auto Listen for 100BASE-TX Negotiation Idles Join Flow Link Mode Set ? Yes Link Mode Set Figure 1. Auto-Negotiation Flow Chart 19 KSZ8041TL/FTL Listen for 10BASE-T Link Pulses No M9999-042707-1.1 ...

Page 20

... INTRP (pin 21 optional interrupt signal that is used to inform the external controller that there has been a status update in the KSZ8041TL/FTL PHY register. Bits[15:8] of register 1Bh are the interrupt control bits, and are used to enable and disable the conditions for asserting the INTRP signal. Bits[7:0] of register 1Bh are the interrupt status bits, and are used to indicate which interrupt conditions have occurred ...

Page 21

... Micrel, Inc. MII Signal Definition The following table describes the MII signals. Refer to Clause 22 of the IEEE 802.3u Specification for detailed information. Direction MII (with respect to PHY, Signal Name KSZ8041TL/FTL signal) TXC Output TXEN Input TXD[3:0] Input RXC Output RXDV Output ...

Page 22

... Provides independent 2-bit wide (di-bit) transmit and receive data paths. • Contains two distinct groups of signals: one for transmission and the other for reception. The KSZ8041TL/FTL is configured in RMII mode after it is power-up or reset with the following: • MHz reference clock connected to REFCLK (pin 15). ...

Page 23

... Micrel, Inc. RMII Signal Definition The following table describes the RMII signals. Refer to RMII Specification for detailed information. Direction RMII (with respect to PHY, Signal Name KSZ8041TL/FTL signal) REF_CLK Input TX_EN Input TXD[1:0] Input CRS_DV Output RXD[1:0] Output RX_ER Output Reference Clock (REF_CLK) REF_CLK is sourced by the MAC or system board ...

Page 24

... Uses 12.5 MHz sync pulse provided by the MAC. • Provides independent single-bit wide transmit and receive data paths for data and control information. The KSZ8041TL/FTL is configured in SMII mode after it is power-up or reset with the following: • A 125 MHz reference clock connected to CLOCK (pin 15). ...

Page 25

... See SMII TXD[0:7] Encoding Table (below) Table 5. SMII TX Bit Description TXD1 TXD2 TXD3 Speed Duplex Link 0=10M 0=Half 0=Down 1=100M 1=Full 1=Up Table 6. SMII TXD[0:7] Encoding Table 25 KSZ8041TL/FTL TXD4 TXD5 TXD6 TXD7 TXD4 TXD5 TXD6 Jabber 1 1 0=No 1=Yes M9999-042707-1.1 TXD7 1 ...

Page 26

... See SMII RXD[0:7] Encoding Table (below) Table 7. SMII RX Bit Description RXD1 RXD2 RXD3 Speed Duplex Link 0=10M 0=Half 0=Down 1=100M 1=Full 1=Up Table 8. SMII RXD[0:7] Encoding Table 26 KSZ8041TL/FTL RXD4 RXD5 RXD6 RXD7 RXD4 RXD5 RXD6 Jabber Upper False Nibble Carrier 0=No Detected 1=Yes ...

Page 27

... HP Auto MDI/MDI-X configuration eliminates the confusion of whether to use a straight cable or a crossover cable between the KSZ8041TL/FTL and its link partner. This feature allows the KSZ8041TL/FTL to use either type of cable to connect with a link partner that is in either MDI or MDI-X mode. The auto-sense function detects transmit and receive pairs from the link partner, and then assigns transmit and receive pairs of the KSZ8041TL/FTL accordingly ...

Page 28

... April 2007 10/100 Ethernet Media Dependent Interface 1 Crossover Receive Pair Cable Transmit Pair Modular Connector (RJ-45) HUB (Repeater or Switch) Figure 5. Typical Crossover Cable Connection 28 10/100 Ethernet Media Dependent Interface 1 Receive Pair Transmit Pair Modular Connector (RJ-45) HUB (Repeater or Switch) KSZ8041TL/FTL M9999-042707-1.1 ...

Page 29

... Power saving mode is disabled by writing a zero to register 1Fh bit 10. Power Down Mode This mode is used to power down the entire KSZ8041TL/FTL device when it is not in use. Power down mode is enabled by writing a one to register 0h bit 11. In the power down state, the KSZ8041TL/FTL disables all internal functions, except for the MII management interface ...

Page 30

... A crystal or clock source, such as an oscillator, is used to provide the reference clock for the KSZ8041TL/FTL. The reference clock is 25 MHz for MII mode, 50 MHz for RMII mode, and 125 MHz for SMII mode. The following three figures illustrate how to connect the reference clock REFCLK / CLOCK (pin 9) and XO (pin 8) of the KSZ8041TL/FTL. 22pF ...

Page 31

... Micrel, Inc. Reference Circuit for Power and Ground Connections The KSZ8041TL/FTL is a single 3.3V supply device with a built-in 1.8V low noise regulator. The power and ground connections are shown in the following figure and table. Figure 9. KSZ8041TL/FTL Power and Ground Connections Power Pin Pin Number V1 ...

Page 32

... By default, FEF is enabled. FEF is disabled by strapping “no FEF” (pin 43) low. See “Strapping Options” section for detail. April 2007 Mode Copper mode Fiber mode No signal detected Far-End Fault generated (if enabled) Fiber mode Signal detected Table 11. Copper and Fiber Mode Selection 32 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 33

... The KSZ8041FTL and KSZ8041TL support MII Back-to-Back mode and RMII Back-to-Back mode for media conversion. MII Back-to-Back Mode The KSZ8041FTL and KSZ8041TL are configured in MII Back-to-Back mode after it is power-up or reset with the following: • CONFIG[2:0] (pins 27, 41, 40) set to ‘110’ for both KSZ8041FTL and KSZ8041TL. ...

Page 34

... Micrel, Inc. RMII Back-to-Back Mode The KSZ8041FTL and KSZ8041TL are configured in RMII Back-to-Back mode after it is power-up or reset with the following: • CONFIG[2:0] (pins 27, 41, 40) set to ‘101’ for both KSZ8041FTL and KSZ8041TL. • A common 50 MHz reference clock connected to REFCLK (pin 15) of both KSZ8041FTL and KSZ8041TL. ...

Page 35

... Electrical isolation of PHY from MII and 0 = Normal operation 0.9 Restart Auto Restart auto-negotiation process Negotiation 0 = Normal operation. This bit is self-cleared after a ‘1’ is written to it. April 2007 ® Control/Status TX+/TX- 35 KSZ8041TL/FTL (1) Default Mode RW/ Set by SPEED strapping pin. See “Strapping Options” section for details. RW Set by NWAYEN strapping pin. See “ ...

Page 36

... PHY ID Assigned to the 3rd through 18th bits of the Number Organizationally Unique Identifier (OUI). Kendin Communication’s OUI is 0010A1 (hex) April 2007 (1) Default Mode RW Set by DUPLEX strapping pin. See “Strapping Options” section for details 000_000 0000 RO/ RO/LL 0 RO/ 0022h 36 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 37

... Symmetric PAUSE [11] = Asymmetric & Symmetric PAUSE April 2007 (1) Default Mode th bits of the RO 0001_01 RO 01_0001 RO 0010 Set by SPEED strapping pin. See “Strapping Options” section for details. RW Set by SPEED strapping pin. See “Strapping Options” section for details 0_0001 KSZ8041TL/FTL M9999-042707-1.1 ...

Page 38

... Logic zero 7.10:0 Message Field 11-bit wide field to encode 2048 messages Register 8h – Link Partner Next Page Ability 8.15 Next Page 1 = Additional Next Page(s) will follow 0 = Last page April 2007 capability capability capability word equaled logic one 38 KSZ8041TL/FTL (1) Default Mode 0_0001 ...

Page 39

... Page Receive 1 = Page Receive occurred Interrupt 0 = Page Receive did not occurred 1b.4 Parallel Detect 1 = Parallel Detect Fault occurred Fault Interrupt 0 = Parallel Detect Fault did not occurred April 2007 word equal to logic zero word equal to logic one Interrupt 39 KSZ8041TL/FTL (1) Default Mode 000_0000_0000 ...

Page 40

... Remote 0 = Normal mode loopback 1 = Remote (analog) loop back is enable 1e.6:0 Reserved April 2007 has completed, this bit is self-cleared. has completed and the status information is valid for read. cable cable LED0 : Link/Activity LED0 : Link 40 KSZ8041TL/FTL (1) Default Mode RO/SC 0 RO/SC 0 RO/SC 0 RO/SC 0 RW/ ...

Page 41

... Enable SQE 1 = Enable SQE test test 0 = Disable SQE test April 2007 Transmit on TX+/- (pins 12,11) and Receive on RX+/- (pins 10,9) Transmit on RX+/- (pins 10,9) and Receive on TX+/- (pins 12,11) pair 41 KSZ8041TL/FTL (1) Default Mode ...

Page 42

... Micrel, Inc. Address Name Description 1f.0 Disable Data 1 = Disable scrambler Scrambling 0 = Enable scrambler Note Read/Write Read only Self-cleared Latch high Latch low. April 2007 (1) Default Mode KSZ8041TL/FTL M9999-042707-1.1 ...

Page 43

... Peak-to-peak 100Ω termination across differential output Peak-to-peak 5MHz square wave 43 ( .......................... +3.135V to +3.465V DDIO_3.3, DDA_3.3 ) .............................. 0°C to +70°C A Max) ................. 125° ....................................69.64°C/W JA Min Typ 2.0 -10 2.4 0. 0.65 0.7 2.2 25 400 KSZ8041TL/FTL Max Units 0 µ µA 1. 0.5 ns ± 0. 1 ...

Page 44

... Specification for packaged product only Current consumption is for the single 3.3V supply KSZ8041TL/FTL device only, and includes the 1.8V supply voltage (V provided by the KSZ8041TL/FTL. The PHY port’s transformer consumes an additional 45mA @ 3.3V for 100Base-TX and 70mA @ 3.3V for 10Base-T. April 2007 ...

Page 45

... SQEP Figure 11. MII SQE Timing (10Base-T) Description TXC period TXC pulse width low TXC pulse width high COL (SQE) delay after TXEN de-asserted COL (SQE) pulse duration Table 14. MII SQE Timing (10Base-T) Parameters 45 KSZ8041TL/FTL Min Typ Max Unit 400 ns 200 ns 200 ns 2 ...

Page 46

... TXD[3:0] hold from rising edge of TXC TXEN hold from rising edge of TXC TXEN high to CRS asserted latency TXEN low to CRS de-asserted latency Table 15. MII Transmit Timing (10Base-T) Parameters CRS2 Min Typ Max Unit 400 ns 200 ns 200 Bit Time 8 Bit Time KSZ8041TL/FTL M9999-042707-1.1 ...

Page 47

... Figure 13. MII Receive Timing (10Base-T) Description RXC period RXC pulse width low RXC pulse width high (RXD[3:0], RXER, RXDV) output delay from rising edge of RXC CRS to (RXD[3:0], RXER, RXDV) latency Table 16. MII Receive Timing (10Base-T) Parameters 47 KSZ8041TL/FTL Min Typ Max Unit 400 ns 200 ns 200 ns ...

Page 48

... TXD[3:0] setup to rising edge of TXC TXEN setup to rising edge of TXC TXD[3:0] hold from rising edge of TXC TXEN hold from rising edge of TXC TXEN high to CRS asserted latency TXEN low to CRS de-asserted latency Table 17. MII Transmit Timing (100Base-TX) Parameters 48 KSZ8041TL/FTL Min Typ Max Unit ...

Page 49

... Figure 15. MII Receive Timing (100Base-TX) Description RXC period RXC pulse width low RXC pulse width high (RXD[3:0], RXER, RXDV) output delay from rising edge of RXC CRS to (RXD[3:0], RXER, RXDV) latency Table 18. MII Receive Timing (100Base-TX) Parameters 49 KSZ8041TL/FTL Min Typ Max Unit ...

Page 50

... April 2007 tcyc t1 t2 Figure 16. RMII Timing – Data Received from RMII tcyc tod Figure 17. RMII Timing – Data Input to RMII Description Min Clock cycle Setup time 4 Hold time 2 Output delay 2.8 Table 19. RMII Timing Parameters 50 KSZ8041TL/FTL Typ Max Unit M9999-042707-1.1 ...

Page 51

... FLP Burst to FLP Burst FLP Burst width Clock/Data Pulse width Clock Pulse to Data Pulse Clock Pulse to Clock Pulse Number of Clock/Data Pulse per FLP Burst rst Min Typ Max 100 55.5 64 69.5 111 128 139 17 33 KSZ8041TL/FTL lse Units µs µs M9999-042707-1.1 ...

Page 52

... MDIO (PHY input) hold from rising edge of MDC MD2 t MDIO (PHY output) delay from rising edge of MDC MD3 April 2007 MD1 MD2 Valid Data t MD3 Figure 19. MDC/MDIO Timing Table 21. MDC/MDIO Timing Parameters 52 KSZ8041TL/FTL Valid Data Valid Data Min Typ Max Unit 400 222 ns M9999-042707-1.1 ...

Page 53

... Micrel, Inc. Reset Timing The KSZ8041TL/FTL reset timing requirement is summarized in the following figure and table. Supply Voltage RST# Strap-In Value Strap-In / Output Pin Parameter After the de-assertion of reset recommended to wait a minimum of 100µs before starting programming on the MIIM (MDC/MDIO) Interface. April 2007 ...

Page 54

... Micrel, Inc. Reset Circuit The following reset circuit is recommended for powering up the KSZ8041TL/FTL if reset is triggered by the power supply. KSZ8041TL/FTL The following reset circuit is recommended for applications where reset is driven by another device (e.g., CPU or FPGA). At power-on-reset and D1 provide the necessary ramp rise time to reset the KSZ8041TL/FTL device. The RST_OUT_n from CPU/FPGA provides the warm reset after power up ...

Page 55

... The following figure shows the reference circuits for pull-up, float and pull-down on the LED1 and LED0 strapping pins. April 2007 Pull-up KSZ8041TL/FTL LED pin Float KSZ8041TL/FTL LED pin Pull-down KSZ8041TL/FTL LED pin Figure 23. Reference Circuits for LED Strapping Pins 55 KSZ8041TL/FTL 3.3V 3.3V 3.3V M9999-042707-1.1 ...

Page 56

... Table 24. Qualified Single Port Magnetics Value 25 ± Table 25. Typical Reference Crystal Characteristics 56 Test Condition 100mV, 100kHz, 8mA 1MHz (min.) 0MHz – 65MHz Auto MDI-X Number of Port Yes 1 Yes 1 Yes 1 Yes 1 Yes 1 Yes 1 Yes 1 Yes 1 Yes 1 Units MHz ppm pF Ω KSZ8041TL/FTL M9999-042707-1.1 ...

Page 57

... Micrel, Inc. Package Information Note: ALL DIMENSIONS ARE IN MILLIMETERS. April 2007 48-Pin (7mm x 7mm) TQFP Package 57 KSZ8041TL/FTL M9999-042707-1 ...

Page 58

... A Purchaser’s use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser’s own risk and Purchaser agrees to April 2007 fully indemnify Micrel for any damages resulting from such use or sale. © 2007 Micrel, Incorporated. 58 KSZ8041TL/FTL M9999-042707-1.1 ...