MCIMX515CJM6C Freescale Semiconductor, MCIMX515CJM6C Datasheet - Page 89

MCIMX515CJM6C

Manufacturer Part Number

MCIMX515CJM6C

Description

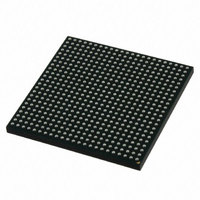

MULTIMEDIA PROC 529-LFBGA

Manufacturer

Freescale Semiconductor

Series

i.MX51r

Datasheets

1.MCIMX512DJM8C.pdf

(200 pages)

2.MCIMX515DJM8C.pdf

(2 pages)

3.MCIMX512CJM6C.pdf

(198 pages)

Specifications of MCIMX515CJM6C

Core Processor

ARM Cortex-A8

Core Size

32-Bit

Speed

600MHz

Connectivity

1-Wire, EBI/EMI, Ethernet, I²C, IrDA, MMC, SPI, SSI, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, POR, PWM, WDT

Number Of I /o

128

Program Memory Type

ROMless

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

0.8 V ~ 1.15 V

Oscillator Type

External

Operating Temperature

-20°C ~ 85°C

Package / Case

529-LFBGA

Processor Series

i.MX51

Core

ARM Cortex A8

Data Bus Width

32 bit

Program Memory Size

36 KB

Data Ram Size

128 KB

Interface Type

I2C, SPI, SSI, UART, USB

Maximum Clock Frequency

200 MHz

Number Of Timers

5

Operating Supply Voltage

0.8 V to 1.15 V

Maximum Operating Temperature

+ 95 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

MCIMX51EVKJ

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCIMX515CJM6C

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MCIMX515CJM6C

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MCIMX515CJM6CR2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

All synchronous display controls are generated on base of an internal generated “local start point”. The

synchronous display controls can be placed on time axis with DI’s offset, up and down parameters. The

display access can be whole number of DI clock (Tdiclk) only. The IPP_DATA can not be moved relative

to the local start point.

4.7.8.5.2

Figure 52

signals are shown with negative polarity. The sequence of events for active matrix interface timing is:

4.7.8.5.3

Figure 53

the data. All shown on the figure parameters are programmable. All controls are started by corresponding

Freescale Semiconductor

•

•

•

•

•

•

•

VSYNC

HSYNC

IPP_DISP_CLK

HSYNC

DRDY

VSYNC—Vertical synchronization

DRDY—Active data

DI_CLK internal DI clock, used for calculation of other controls.

IPP_DISP_CLK latches data into the panel on its negative edge (when positive polarity is

selected). In active mode, IPP_DISP_CLK runs continuously.

HSYNC causes the panel to start a new line. (Usually IPP_PIN_2 is used as HSYNC)

VSYNC causes the panel to start a new frame. It always encompasses at least one HSYNC pulse.

(Usually IPP_PIN_3 is used as VSYNC)

DRDY acts like an output enable signal to the CRT display. This output enables the data to be

shifted onto the display. When disabled, the data is invalid and the trace is off.

(For DRDY can be used either synchronous or asynchronous generic purpose pin as well.)

IPP_DATA

depicts the LCD interface timing for a generic active matrix color TFT panel. In this figure

depicts the horizontal timing (timing of one line), including both the horizontal sync pulse and

LCD Interface Functional Description

TFT Panel Sync Pulse Timing Diagrams

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 4

Figure 52. Interface Timing Diagram for TFT (Active Matrix) Panels

LINE 1

1

LINE 2

2

LINE 3

3

LINE 4

LINE n-1

m-1

Electrical Characteristics

LINE n

m

89