ATTINY461V-10MU Atmel, ATTINY461V-10MU Datasheet - Page 26

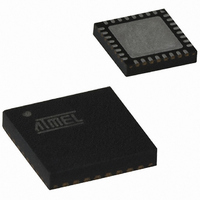

ATTINY461V-10MU

Manufacturer Part Number

ATTINY461V-10MU

Description

IC MCU AVR 4K FLASH 10MHZ 32-QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY461V-10MU

Core Processor

AVR

Core Size

8-Bit

Speed

10MHz

Connectivity

USI

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

16

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 11x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-VQFN Exposed Pad, 32-HVQFN, 32-SQFN, 32-DHVQFN

Processor Series

ATTINY4x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

2-Wire, SPI, USI

Maximum Clock Frequency

10 MHz

Number Of Programmable I/os

16

Number Of Timers

2

Operating Supply Voltage

1.8 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 16 Channel

Package

32MLF EP

Device Core

AVR

Family Name

ATtiny

Maximum Speed

10 MHz

For Use With

ATSTK600 - DEV KIT FOR AVR/AVR32ATAVRBC100 - REF DESIGN KIT BATTERY CHARGER770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAG

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY461V-10MUR

Manufacturer:

Atmel

Quantity:

9 818

- Current page: 26 of 242

- Download datasheet (5Mb)

6.2.1

6.2.2

26

ATtiny261/461/861

External Clock

High-Frequency PLL Clock

mencing normal operation. The watchdog oscillator is used for timing this real-time part of the

start-up time. The number of WD oscillator cycles used for each time-out is shown in

Table 6-2.

To drive the device from an external clock source, CLKI should be driven as shown in

2. To run the device on an external clock, the CKSEL Fuses must be programmed to “0000”.

Figure 6-2.

When this clock source is selected, start-up times are determined by the SUT Fuses as shown in

Table

Table 6-3.

When applying an external clock, it is required to avoid sudden changes in the applied clock fre-

quency to ensure stable operation of the MCU. A variation in frequency of more than 2% from

one clock cycle to the next can lead to unpredictable behavior. It is required to ensure that the

MCU is kept in Reset during such changes in the clock frequency.

Note that the system clock prescaler can be used to implement run-time changes of the internal

clock frequency. See

The internal PLL generates a clock signal with a frequency eight times higher than the source

input. The PLL uses the output of the internal 8 MHz oscillator as source and the default setting

generates a fast peripheral clock signal of 64 MHz.

SUT1:0

00

01

10

11

6-3.

Typ Time-out

Start-up Time from Power-

Number of Watchdog Oscillator Cycles

External Clock Drive Configuration

Start-up Times for the External Clock Selection

EXTERNAL

down and Power-save

64 ms

4 ms

SIGNAL

CLOCK

“System Clock Prescaler” on page 31

6 CK

6 CK

6 CK

Additional Delay from

Reserved

14CK + 64 ms

14CK + 4 ms

Reset

14CK

CLKI

GND

for details.

Number of Cycles

8K (8,192)

512

BOD enabled

Fast rising power

Slowly rising power

Recommended Usage

2588E–AVR–08/10

Table

Figure 6-

6-2.

Related parts for ATTINY461V-10MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 4K 20MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 4K FLASH 20MHZ 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4K FLASH 15MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4KB FLASH 15MHZ 32-VQFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4KB FLASH 20MHZ 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 4K 20MHZ 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 4kB Flash 0.256kB EEPROM 16 I/O Pins

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 2K FLASH, 20SOIC

Manufacturer:

Atmel

Datasheet: